Precise Alignment and Decal Bonding of a Pattern of Solder Preforms to a Surface

a technology of precision alignment and decal bonding, which is applied in the direction of soldering apparatus, semiconductor/solid-state device details, manufacturing tools, etc., can solve the problems of limiting the processing speed of pick-and-place systems, slow manual placement, and affecting the accuracy of solder pattern placement, etc., to achieve high spatial accuracy, high precision, and high placement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

Decal Imprinting and Bonding of Solder (DIBS)

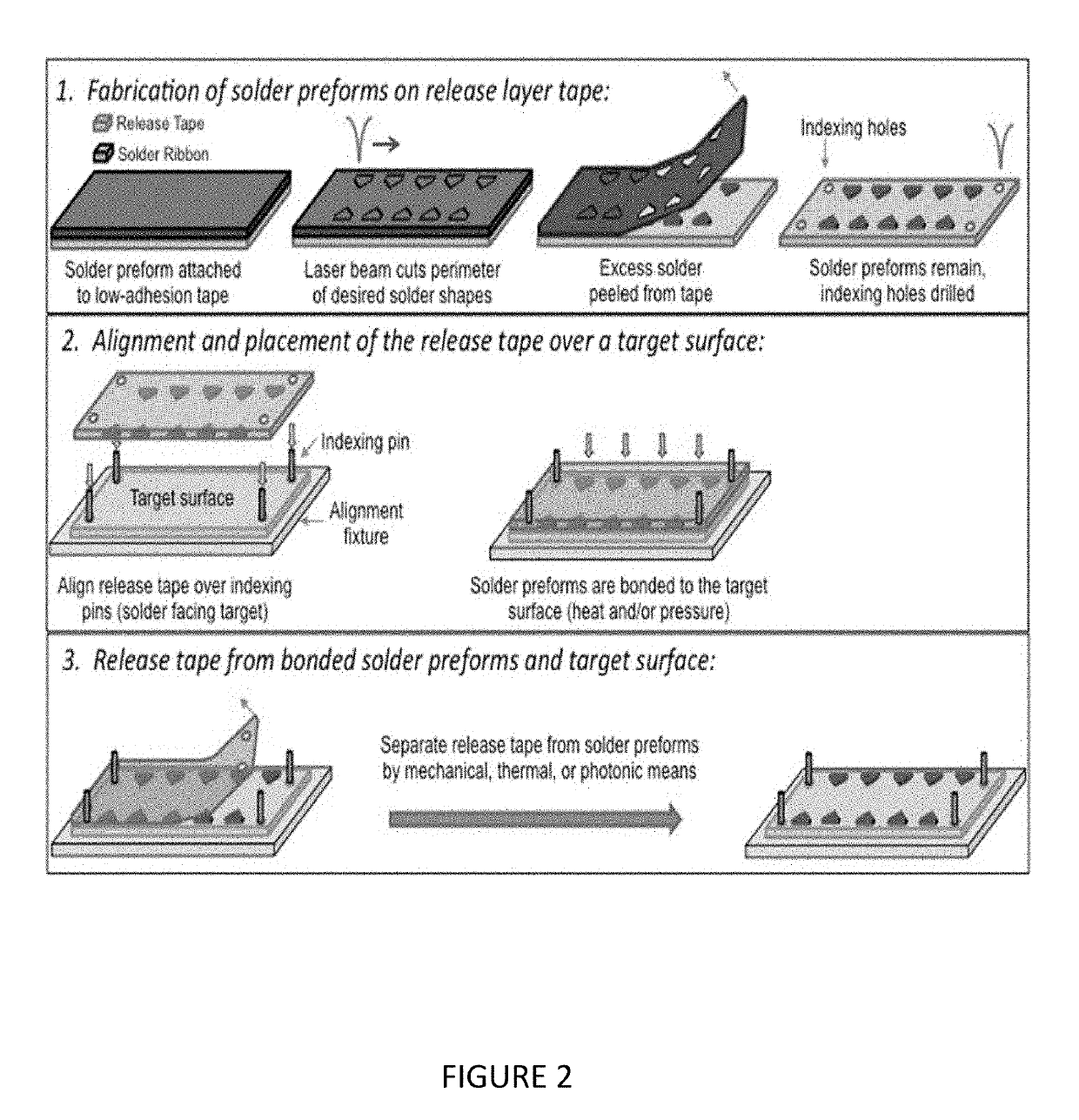

[0032]This invention, which can be termed “Decal Imprinting and Bonding of Solder” (DIBS) consists of three steps—the fabrication of the solder preforms (shape and spacing) on the release (layer or) tape, the alignment and placement of the release tape over a target surface, and release of the individual solder preforms from the release tape onto the target surface and their subsequent bonding to the target surface.

[0033]The solder preforms can be detached from the release tape and bonded to the target surface by mechanical, thermal or photonic means.

example 2

[0034]To fabricate the solder release tape, a strip of semiconductor dicing tape, such as ‘low-tack blue’ is used as the support structure for the solder preforms. Components attached to low tack blue' dicing tape can be removed mechanically. Other types of dicing tape can use heat (Nitto “Revalpha”) or UV light (DU-300) to lower its adhesion properties in order to release its attached components.

[0035]A strip of dicing or release tape about the same size and shape as the target surface is secured to a stable surface, for example a vacuum chuck.

[0036]Next, a ribbon of solder of fixed thickness (e.g. Indium Bismuth eutectic) is pressed onto the release tape.

[0037]A UV (λ=355 nm) laser is then focused onto the solder and perforates the perimeter or outline of the desired solder preforms without damaging the underlying release tape.

[0038]To ensure precise alignment of the release tape (and the solder preforms) to the target surface, the same laser is used to drill indexing holes into t...

example 3

[0040]This solder preform tape can now be guided over the corresponding indexing pins of an alignment jig, which holds the receiving surface, and the solder side placed over and pressed onto receiving surface.

[0041]Solder preforms such as In2Bi, can be mechanically released from the dicing tape and pressure and thermally treated to bond to a compatible surface in a single step.

[0042]The release tape can then be removed leaving behind a precisely spaced pattern of solder preforms on the target surface. Note that additional layers or tapes with the same pattern of indexing holes can now be precisely aligned and placed over this first layer of solder preforms. FIG. 1 shows a finished blue ‘low tack’ release tape with a set of solder preforms ready for use.

[0043]This invention enables multiple solder preforms of arbitrary size and shape to be fabricated at precise locations on a release tape. This prescribed pattern of solder preforms matches the location of the corresponding “bond pads...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thick | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More