Semiconductor integrated circuit device and method of manufacturing the same

a technology of integrated circuits and semiconductors, applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of concentrating distortionally on the end of the gate electrode, the electric field does not exhibit a uniform intensity distribution, and the reliability of the eeprom is somewhat inferior, so as to achieve a wide dispersion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

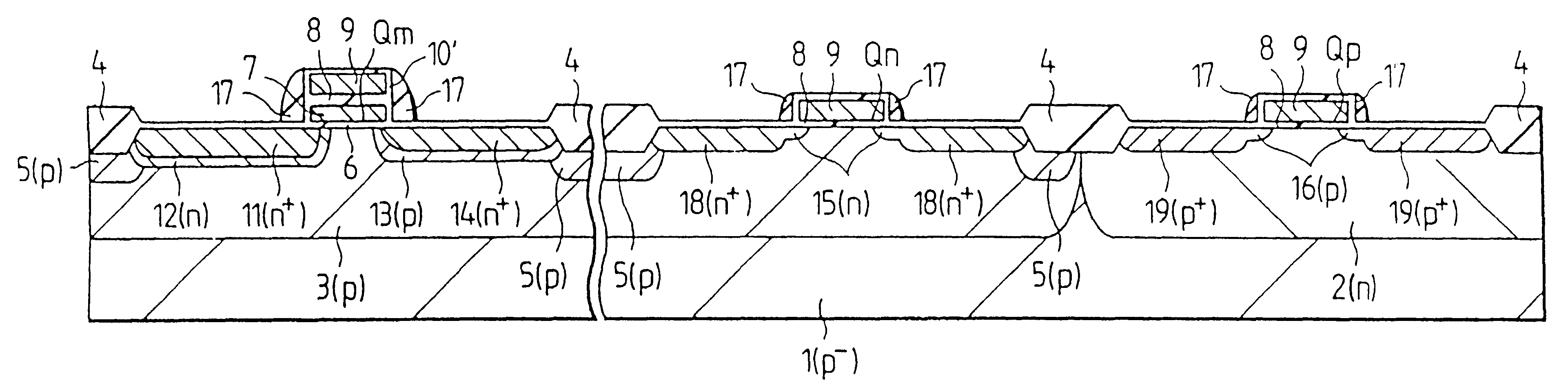

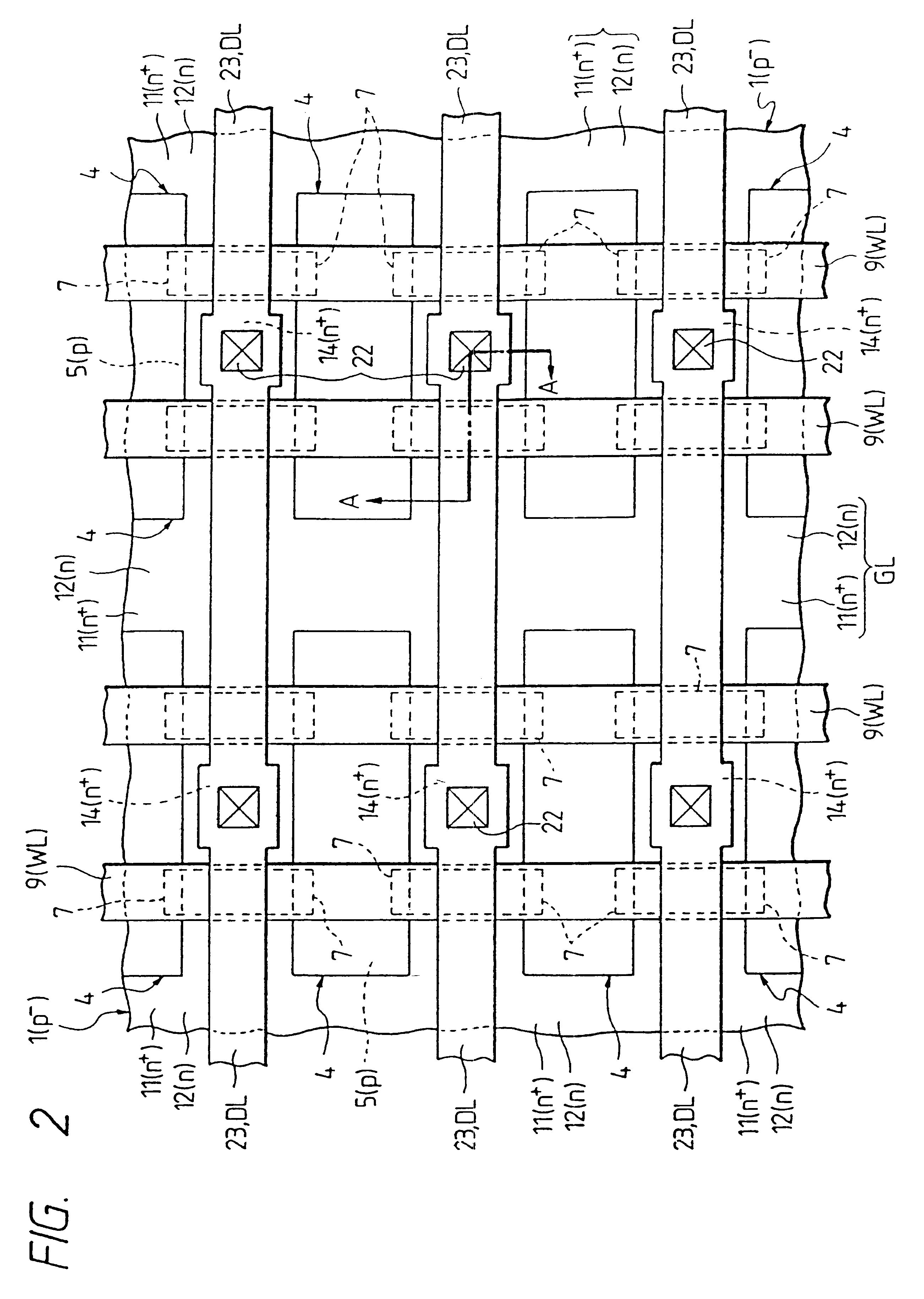

FIG. 3 is a sectional view of p-channel and n-channel MISFETs which constitute the memory cell and peripheral circuit of an EEPROM being the present invention. The section of the memory cell in FIG. 3 is taken along A--A in FIG. 2.

As shown in FIG. 3, the EEPROM is constructed using a p.sup.- -type semiconductor substrate 1 which is made of single-crystal silicon. A p-type well region 3 is provided in the principal surface part of the semiconductor substrate 1 in domains for forming the flash type nonvolatile memory cell Q.sub.m and the n-channel MISFET Q.sub.n while an n-type well region 2 is provided in a domain for forming the p-channel MISFET Q.sub.p.

An insulator film 4 for isolating the elements is provided between the adjacent domains for forming the elements, and on the principal surface parts of the n-type well region 2 and the p-type well region 3. In the principal surface part of the p-type well region 3, a p-type channel stopper region 5 is provided under the element isola...

second embodiment

FIG. 20 shows the schematic construction of a flash type nonvolatile memory cell according to the present invention.

The point of difference from the first embodiment stated before will be described. In the flash type nonvolatile memory cell according to the second embodiment depicted in the Figure, a region 24 of low impurity concentration is locally formed in the vicinity of the part of the front surface of a source region 11 underlying one end of a floating gate electrode 7, thereby to form electric field buffer means for moderating an electric field which is established between the source region 11 and the end of the floating gate electrode 7 during the application of an erasing voltage.

That is, the electric field is moderated in such a way that a depletion layer is rendered liable to spread in the surface part of the source region 11 underlying the end of the floating gate electrode 7.

The low impurity concentration region 24 is formed in such a way that the amount of doping with...

third embodiment

Now, FIG. 31 shows a modification of the third embodiment stated above. A floating gate electrode 7 and a control gate electrode 9 are asymmetric between on the side of a source region 11, 12 and on the side of a drain region 14. In this case, the side of the floating gate electrode 7 near the source region 11, 12 is laterally protruded 0.2-0.3 [.mu.m] beyond the control gate electrode 9 by a side-wall spacer 17 in the same manner as in the foregoing embodiment. In contrast, on the side of the floating gate electrode 17 near the drain region 14, the ends of this electrode 17 and the control gate electrode 9 are vertically aligned so as to be substantially coplanar.

Owing to such an asymmetric structure, the overlap between the source region 11, 12 and the floating gate electrode 7 can be enlarged to enhance erasing characteristics, while at the same time, the overlap between the drain region 14 and the floating gate electrode 7 can be made null or small to enhance writing characteris...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More