Spacer-type thin-film polysilicon transistor for low-power memory devices

a technology of low-power memory and polysilicon, which is applied in the direction of transistors, semiconductor devices, electrical equipment, etc., can solve the problems of difficult manufacturing of devices using such geometries, the small polysilicon grain size of these layers is also very small, and the leakage of bitline to supply (vcc) is still too significant to enable battery operation of high-density memory devices, such as srams, over an extended period of time, so as to minimize the leakag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

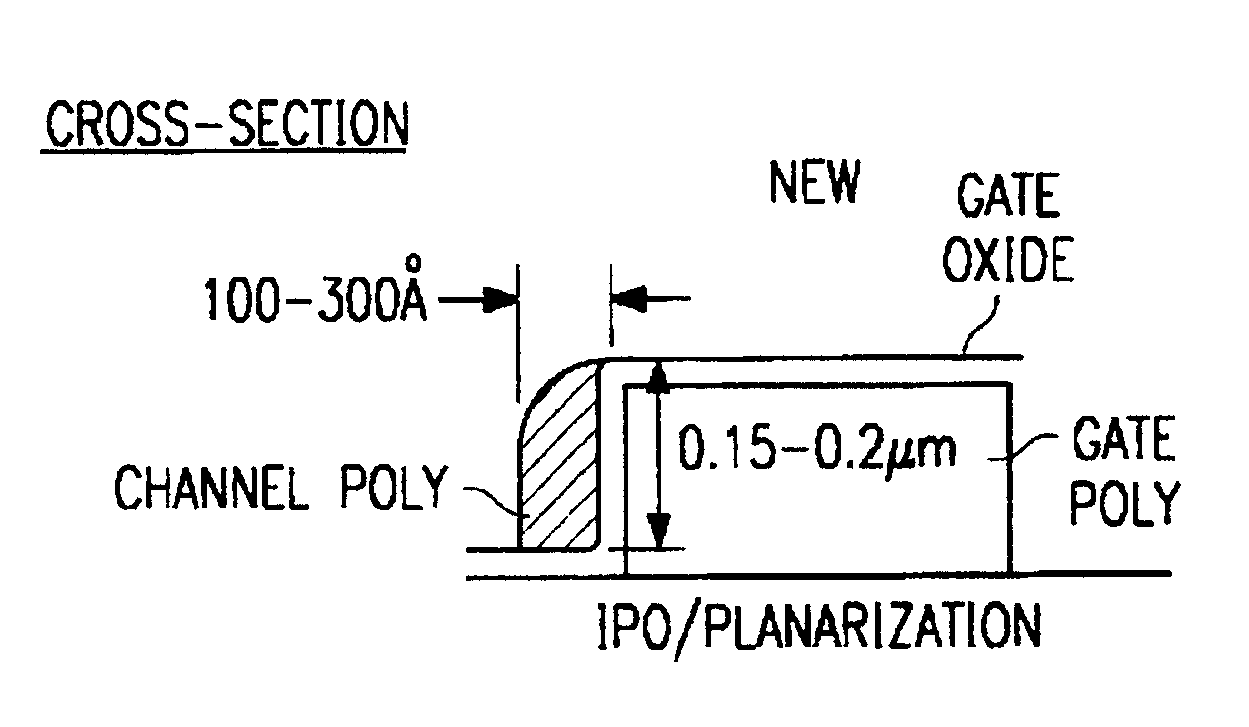

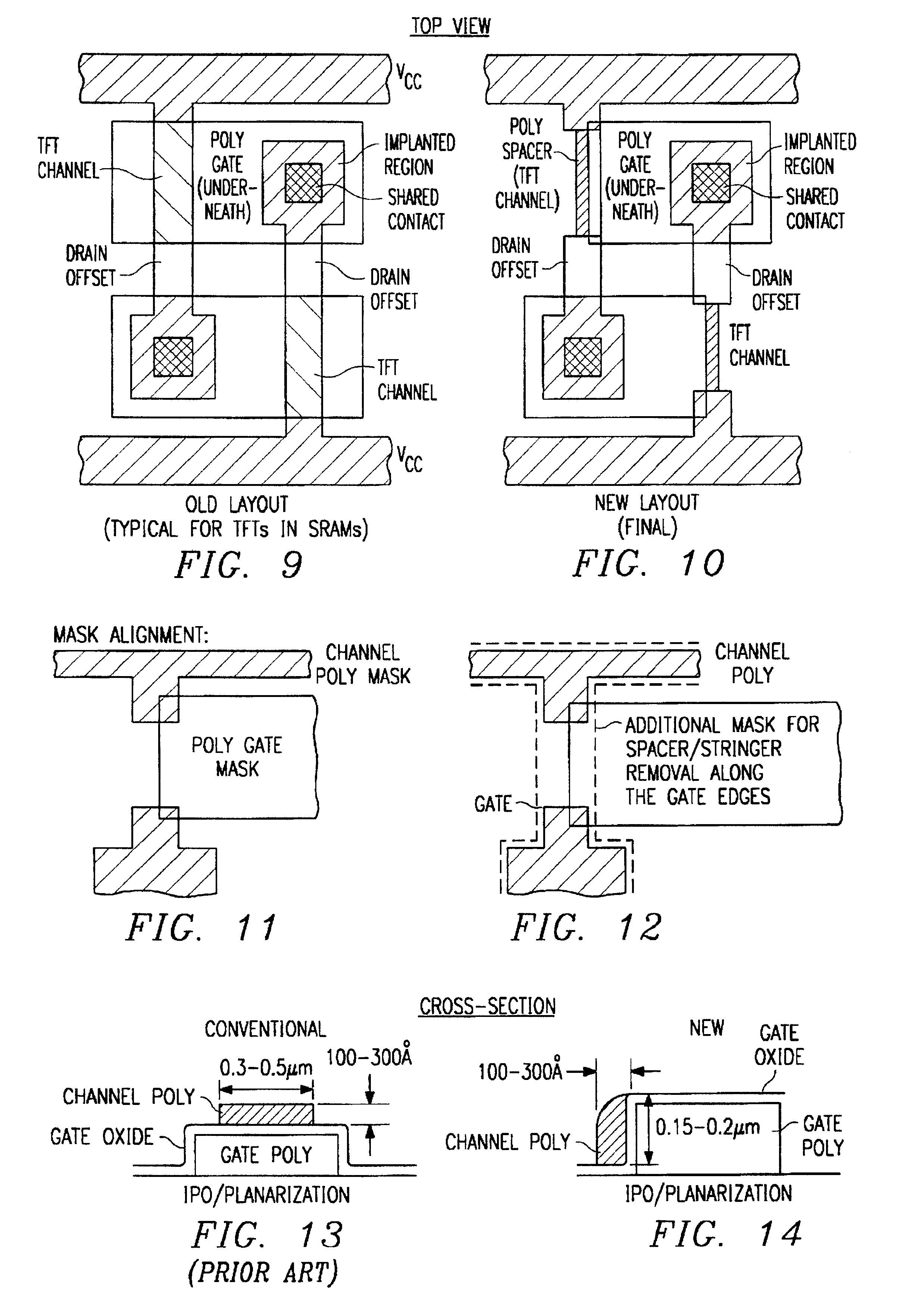

[0023]An understanding of the first preferred embodiment of the present invention is further aided by comparing the cross-sectional view of a conventional TFT structure of FIG. 13 with the cross-sectional view of the present invention shown in FIG. 14. The cross-sectional area of the conventional TFT channel is shown as approximately 0.3 to 0.5 μm by approximately 300 to 500 Å, requiring special lithography tools, as mentioned above. The cross-sectional area of the TFT channel of the present invention is much smaller and is approximately 0.15 to 0.2 μm approximately 300 to 500 Å. This is achieved without any lithography-related constraints.

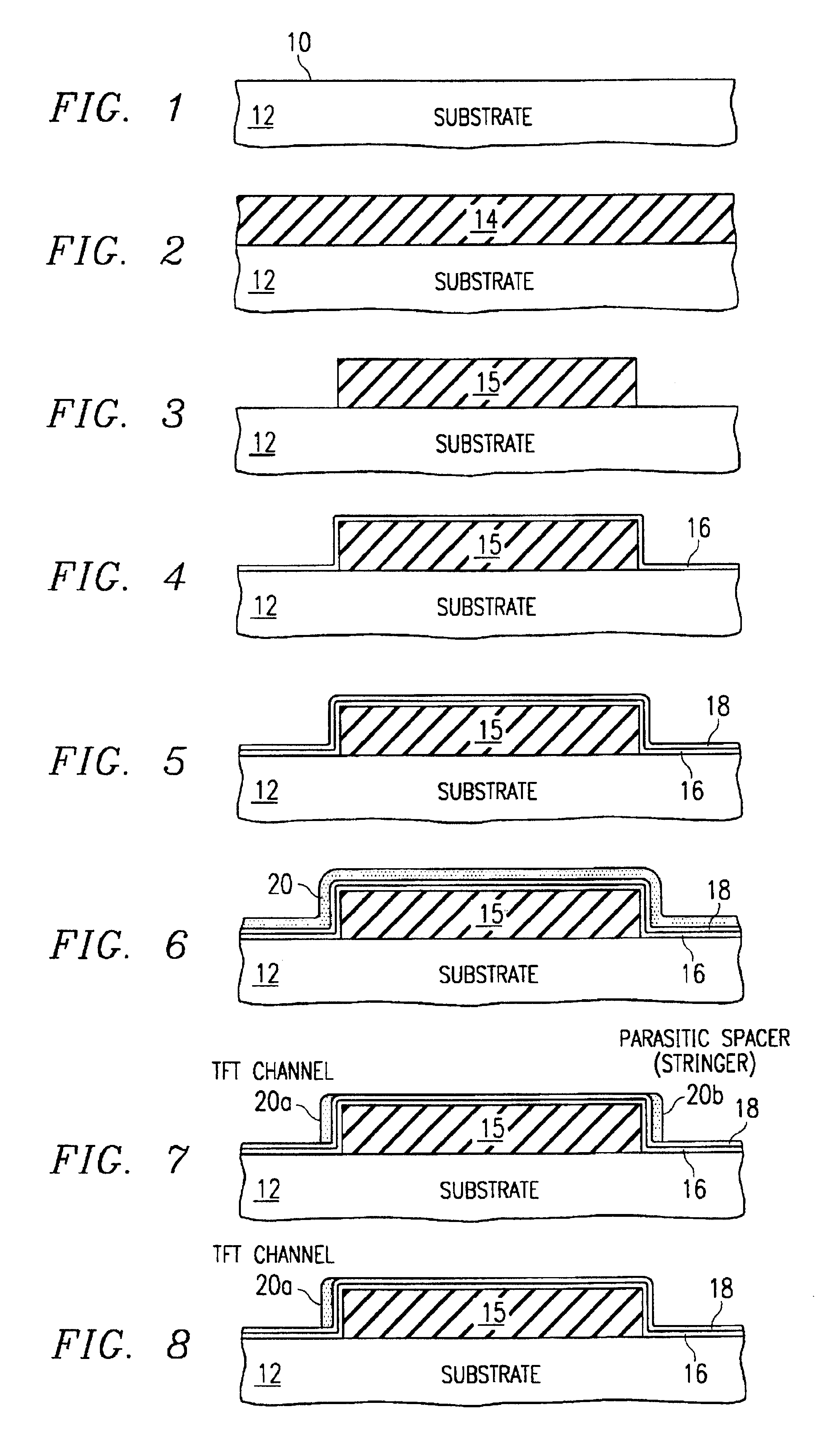

[0024]The process steps and structure of the first preferred embodiment of the present invention, represented in FIGS. 1-14, illustrate a TFT device having a channel that is both very narrow and thin. However, the first preferred embodiment of the present invention requires at least two poly layers: one or two poly layers formed in the standard pr...

second embodiment

[0032]In addition to utilizing only two poly layers rather than three poly layers and not requiring planarization, the present invention offers other desirable features. The simultaneously salicided Vss and Vcc voltage supply lines of the second preferred embodiment allow for reduced series resistance. Additionally the TFT source (P+) connected to the pull-down gate (N+) through the TaSi or WSi layer ensures that there is no problematic N+ / P+ parasitic junction.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More