Semiconductor package with heat dissipating structure

a technology of semiconductor packages and heat dissipation structures, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of affecting the performance and lifetime of the chip, generating heat that cannot be efficiently dissipated, and undesirably damaging the electrical performance and reliability of the package products, etc., to achieve the effect of improving the flexibility of the component arrangement of the semiconductor package, reducing the surface area of the substrate, and increasing the layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

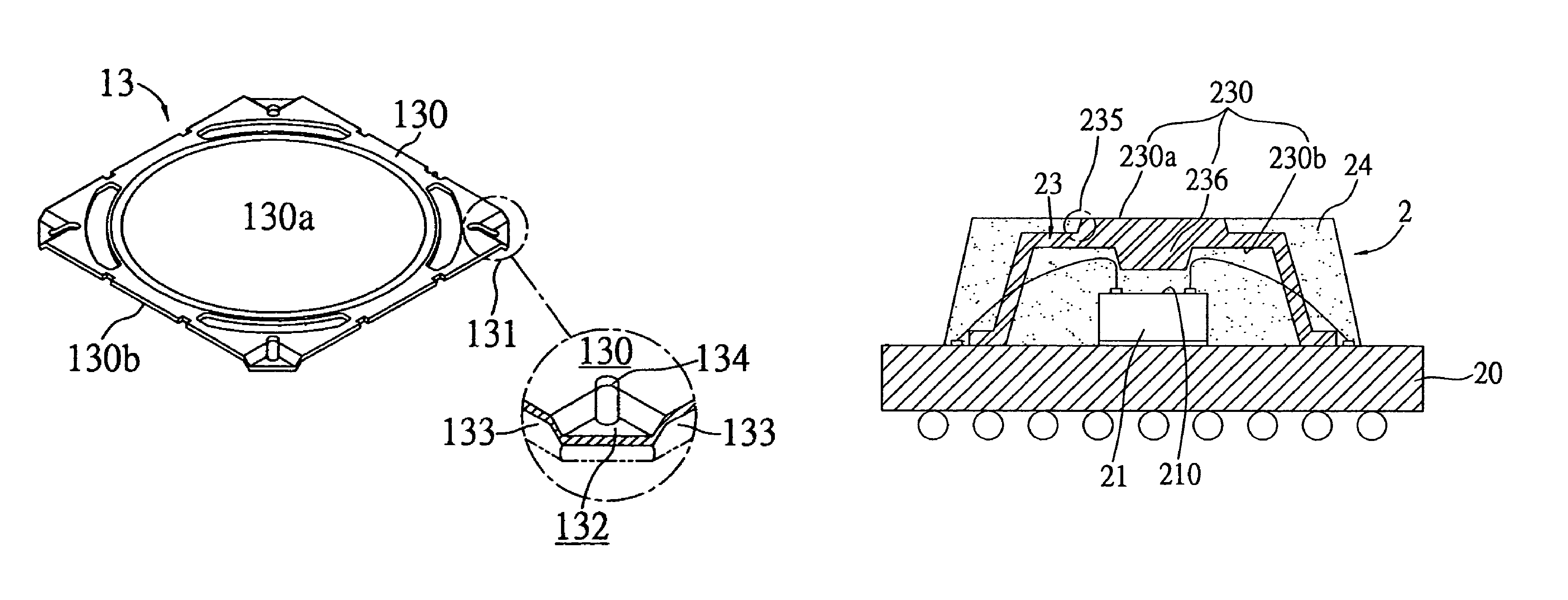

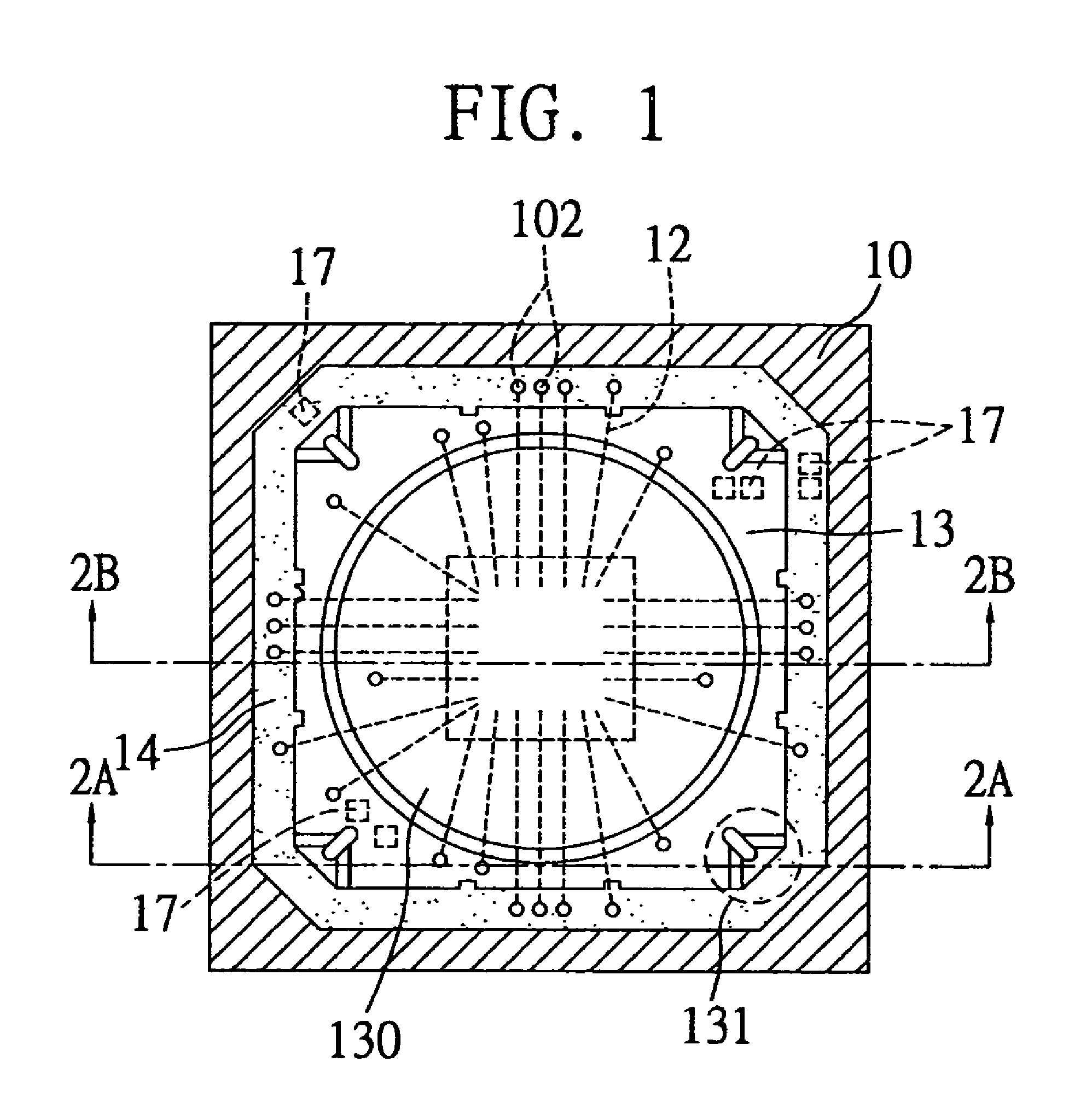

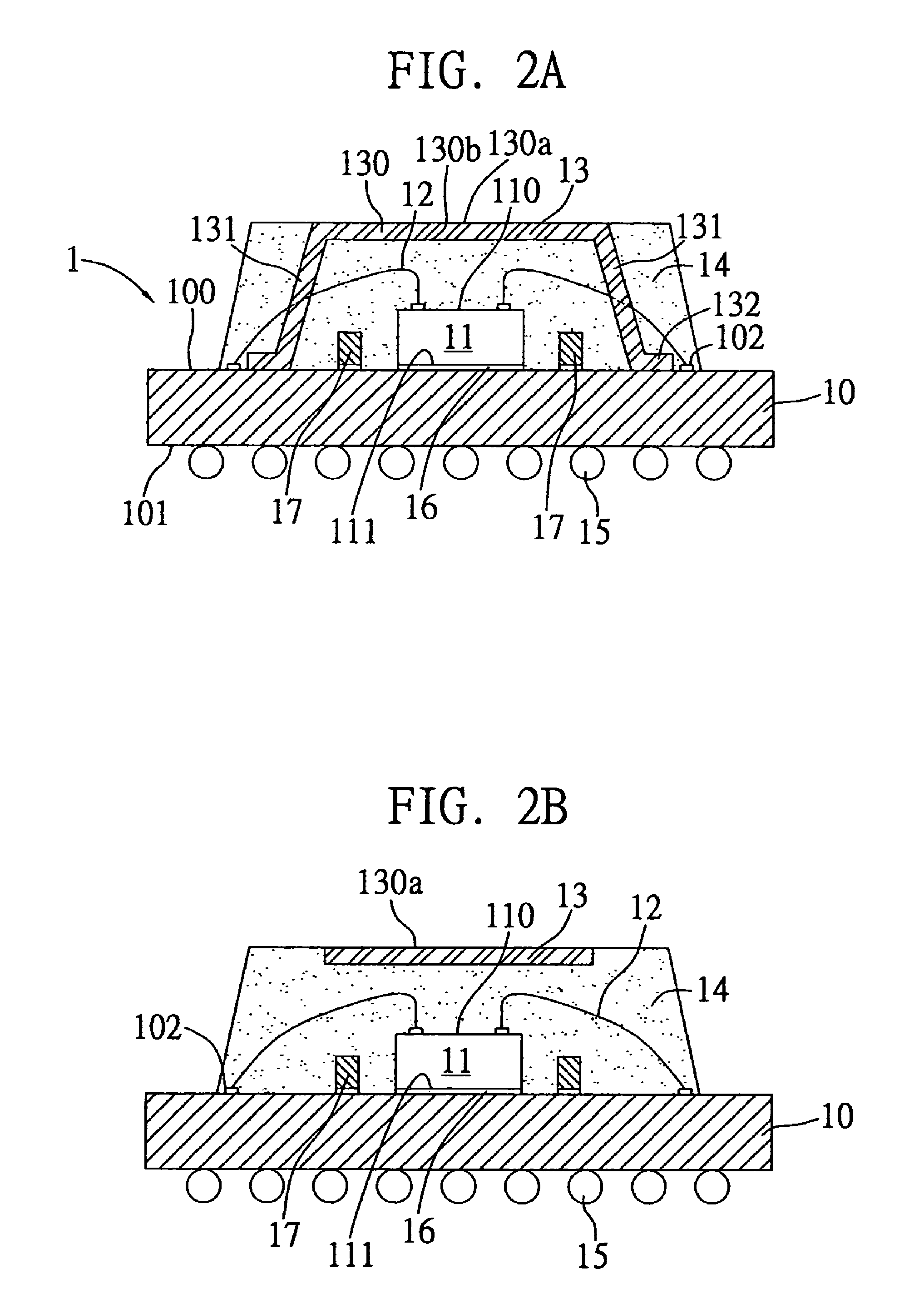

FIGS. 1, 2A and 2B illustrate a semiconductor package 1 proposed in the present invention, wherein FIGS. 2A and 2B are cross-sectional views of the semiconductor package 1 shown in FIG. 1. As shown in the drawings, the semiconductor package 1 comprises: a substrate 10; a chip 11 mounted on the substrate 10; a plurality of bonding wires 12 for electrically connecting the chip 11 to the substrate 10; a heat sink 13 mounted on the substrate 10; a plurality of passive components 17 disposed on the substrate 10; an encapsulant 14 for encapsulating the chip 11, bonding wires 12, heat sink 13 and passive components 17; and a plurality of solder balls 15 implanted on the substrate 10 and exposed to outside of the encapsulant 14.

The substrate 10 has a top surface 100 and a bottom surface 101 opposed to the top surface 100, each surface being formed with predetermined conductive traces (not shown) thereon. A plurality of conventional vias (not shown) are formed through the substrate 10 for el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More