Condition presetting construction based D trigger having scanning test function

A scanning test and flip-flop technology, which is applied in the direction of electronic circuit testing, electrical components, pulse generation, etc., can solve the problem of extreme asymmetry of the rising edge delay and falling edge delay of the output terminal of the flip-flop circuit.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

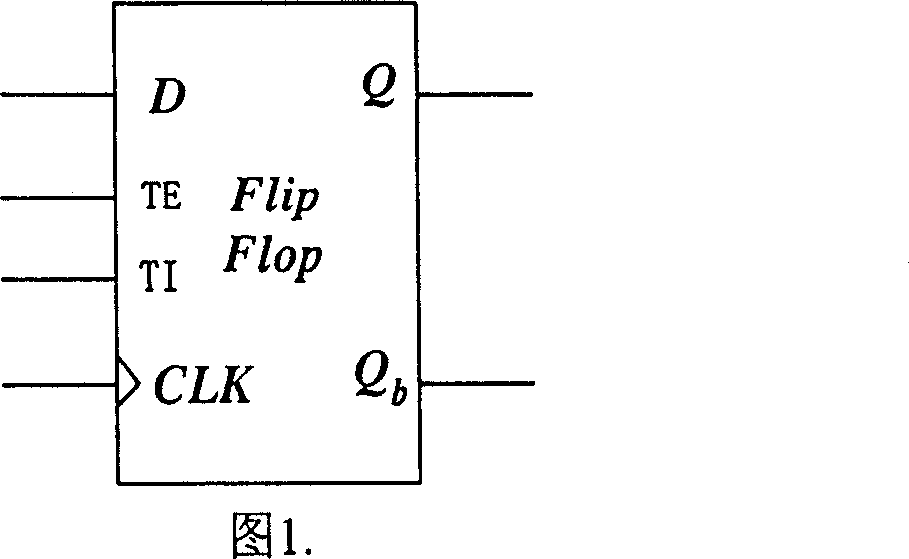

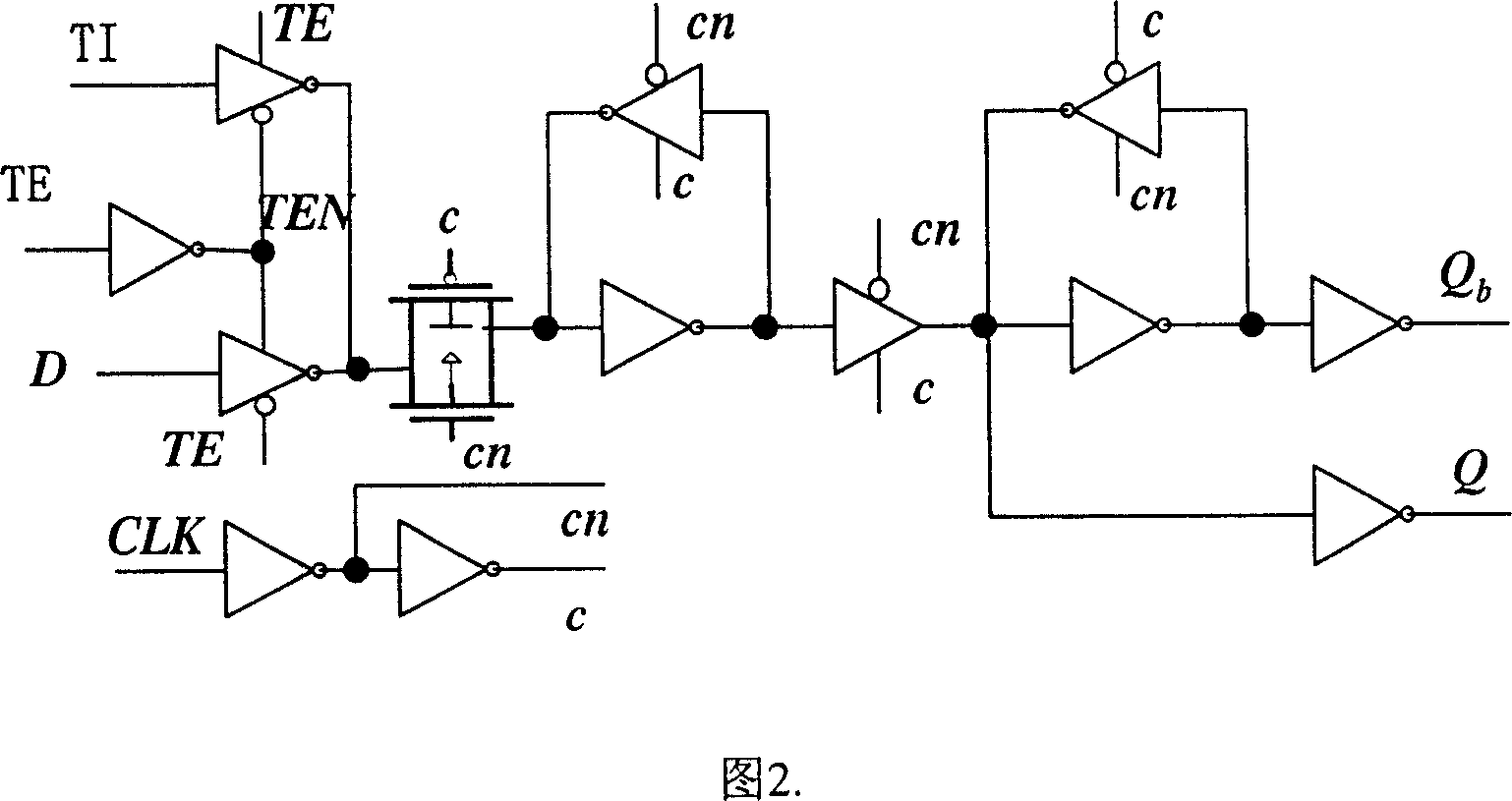

[0074] The technical solution of the present invention to solve the technical problem is: the testable flip-flop FFSDHD1X_SCB_FCS based on the conditional prefill structure proposed by the present invention, as shown in FIG. 4 . The FFSDHD1X_SCB_FCS flip-flop has the feature of using conditional precharge technology to reduce the power consumption of the flip-flop circuit itself, and also has testable functions.

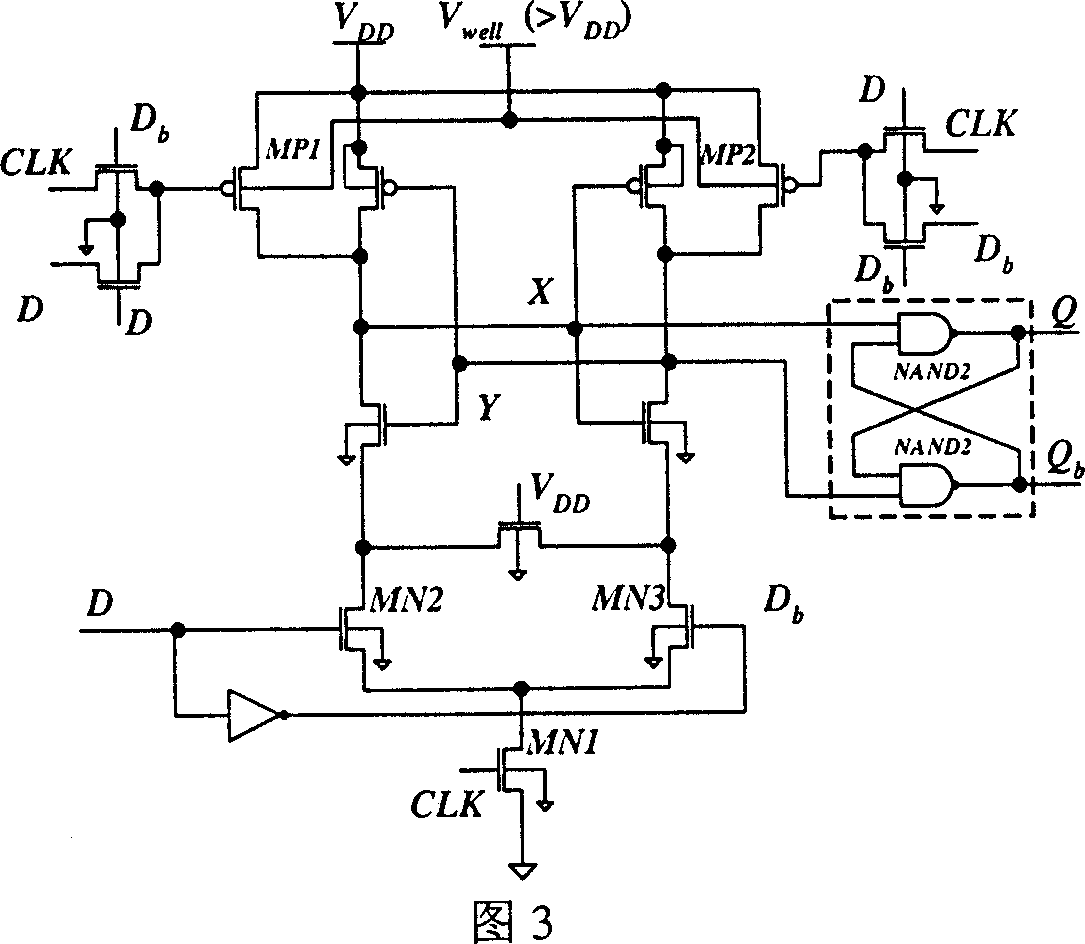

[0075] The structure on the right side in Figure 4 is a basic flip-flop based on the conditional precharge structure. DI is the D signal input terminal of the basic flip-flop, which is a D flip-flop triggered by a rising edge. Its working principle is as follows: the clock signal CLK and the input The data signal DI forms an "OR" logic and is connected to the gate of the PMOS transistor MP1, while the clock signal CLK and the input data signal D b Form OR logic and connect to the gate of PMOS transistor MP2. When CLK is at a high level, both MP1 and MP2 are turned o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More