Test device for masiac storage

An embedded memory and test device technology, applied in static memory, instruments, etc., can solve problems such as waste of chip area and power consumption, and achieve the effect of saving area and power consumption, and saving chip area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

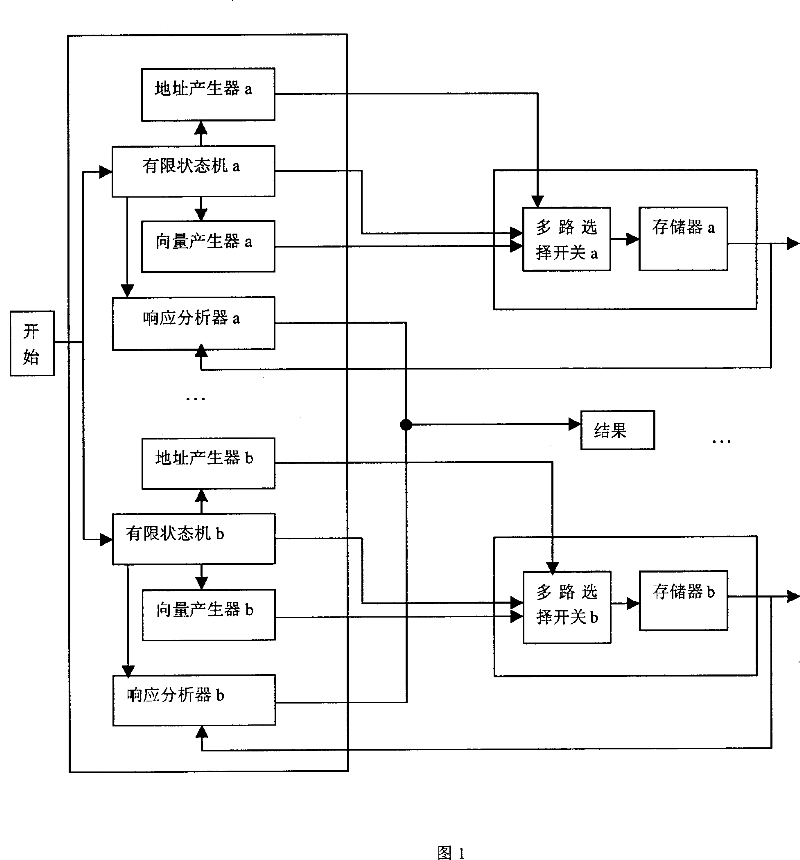

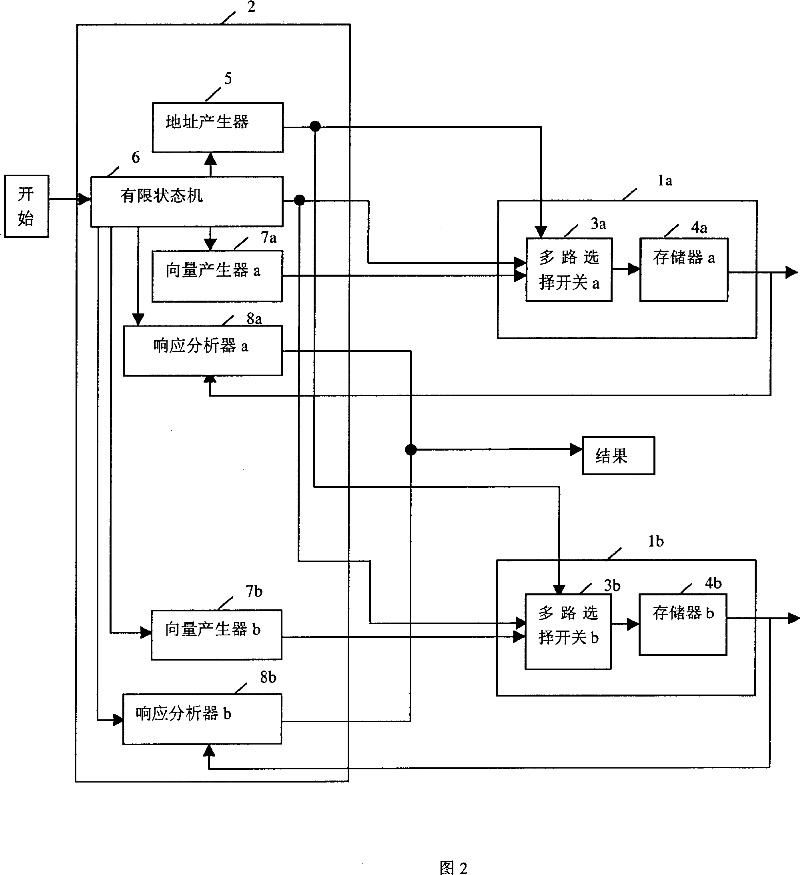

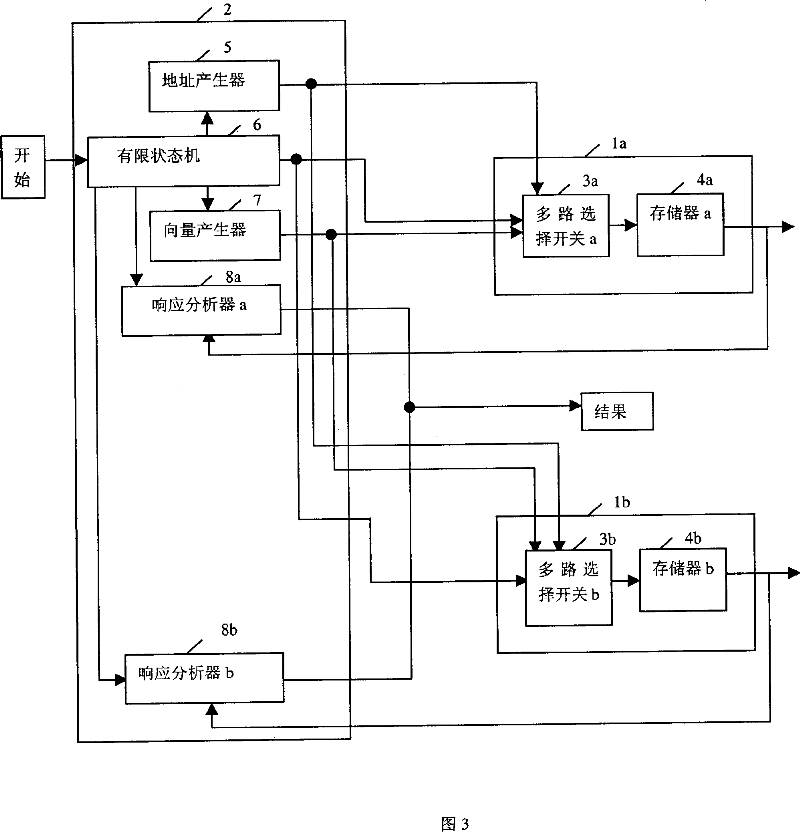

[0022]Referring to Fig. 2, a kind of testing device of embedded memory, comprises 2 groups of memory modules 1a, 1b and the embedded memory test control module 2 that receives chip external pin start signal, memory module 1a includes multiplex switch 3a and memory 4a , the memory module 1b includes a multiplex switch 3b and a memory 4b. The depth of the memory 1a is greater than the depth of the memory 1b. The output terminal of the multiplex switch 3a is connected to the input terminal of the memory 4a. The output end of the multiplex switch 3b is connected to the input end of the memory 4b. The embedded memory test control module 2 includes two response analyzers 8a, 8b and two vector generators 7a, 7b corresponding to the two groups of memory modules 1a, 1b. Described embedded memory test control module 2 comprises an address generator 5 and a finite state machine 6, and described address generator 5 is the address generator corresponding with memory module 1a, and descri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More