Boost clock generation circuit and semiconductor device

A clock generation circuit and clock technology, which is applied in the manufacturing of semiconductor devices, circuits, and semiconductor/solid-state devices, etc., can solve the problems of increasing and weakening the scale of the boost clock circuit, reducing the through current, reducing the current of charging and discharging, Avoid the effect of simultaneous conduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

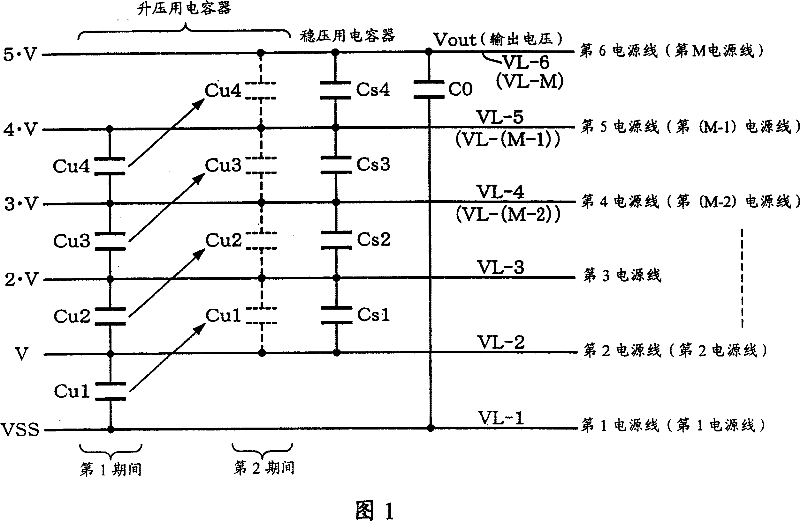

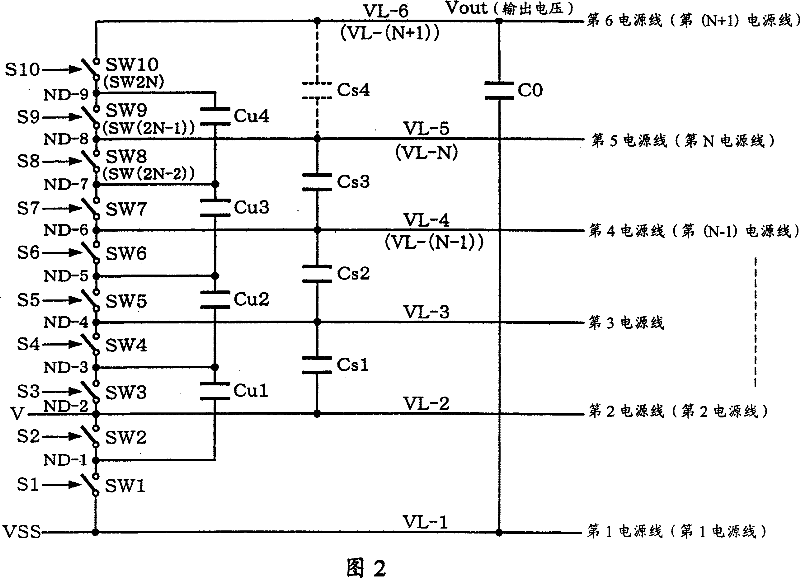

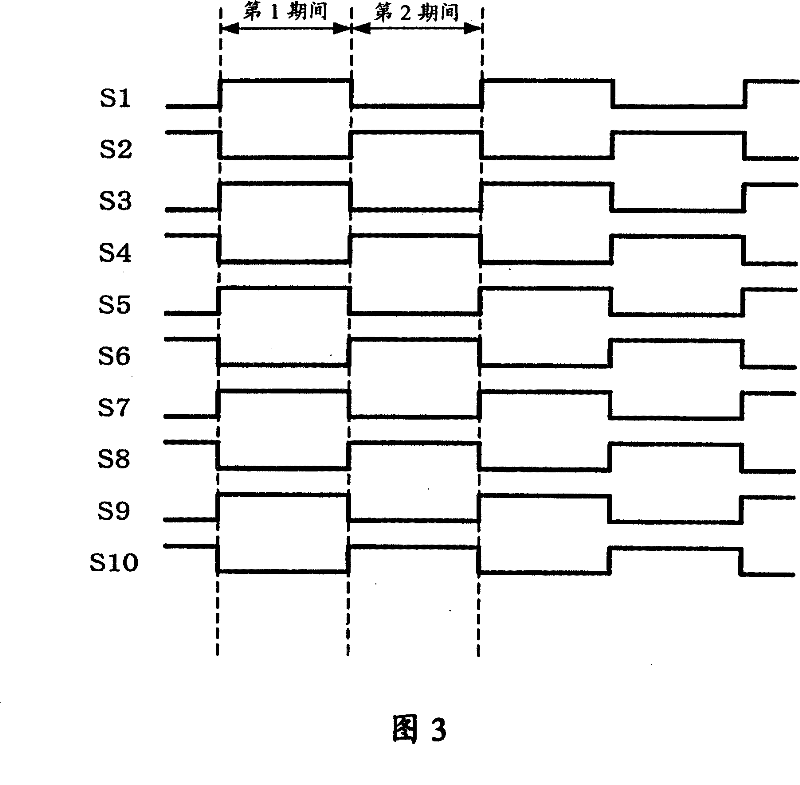

[0063] Preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings. The present embodiment described below does not unduly limit the content of the present invention described in the claims, and not all the configurations described in the present embodiment are necessarily adopted as solutions of the present invention.

[0064] First, a charge pump circuit suitable for inclusion in a semiconductor device (integrated circuit, IC) will be described. Next, a boost clock generating circuit suitable for generating the boost clock of the charge pump circuit will be described.

[0065] 1. Charge pump circuit

[0066] The boosted clock circuit of this embodiment includes at least two capacitors, that is, the boosted voltage is output by the charge pump method.

[0067] FIG. 1 shows an explanatory diagram of the working principle of the charge pump circuit of this embodiment. The charge pump circuit of this embodiment ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More