Formation of lattice-tuning semiconductor substrates

A technology of semiconductors and lattices, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as inappropriate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The following description focuses on the formation of a virtual lattice-tuned Si substrate on an underlying Si substrate with an inserted SiGe buffer layer. However, it should be understood that the present invention is also applicable to the fabrication of other types of lattice-tuned semiconductor substrates, including the fabrication of substrates that allow III-V incorporation of silicon terminated in completely stress-free pure Ge. According to the present invention, one or more surfactants, such as antimony, can also be added during the epitaxial growth process, thereby reducing surface energy to produce a flatter virtual substrate surface and lower density threading dislocations.

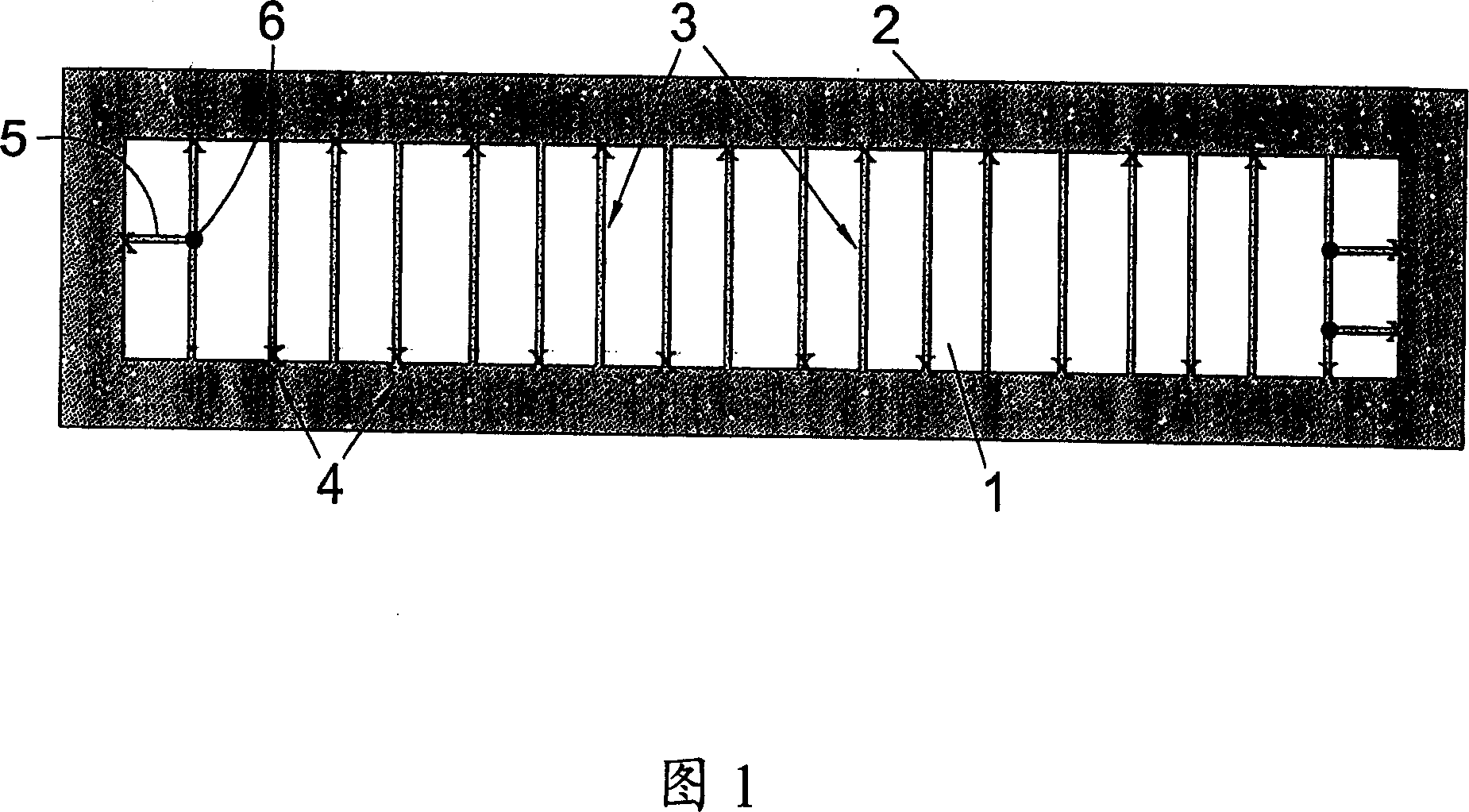

[0019] Figure 1 shows a thin strip 1 of SiGe material grown in an area bounded by silicon oxide walls 2 surrounding four sides of the SiGe material. During the growth of the SiGe layer in said region by epitaxial growth, dislocations 3 are preferentially formed along the shortest direc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More