Film transistor manufacturing method

A technology for thin film transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of inability to form shallow doped drains, etc., and achieve the effect of fewer lithography masks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

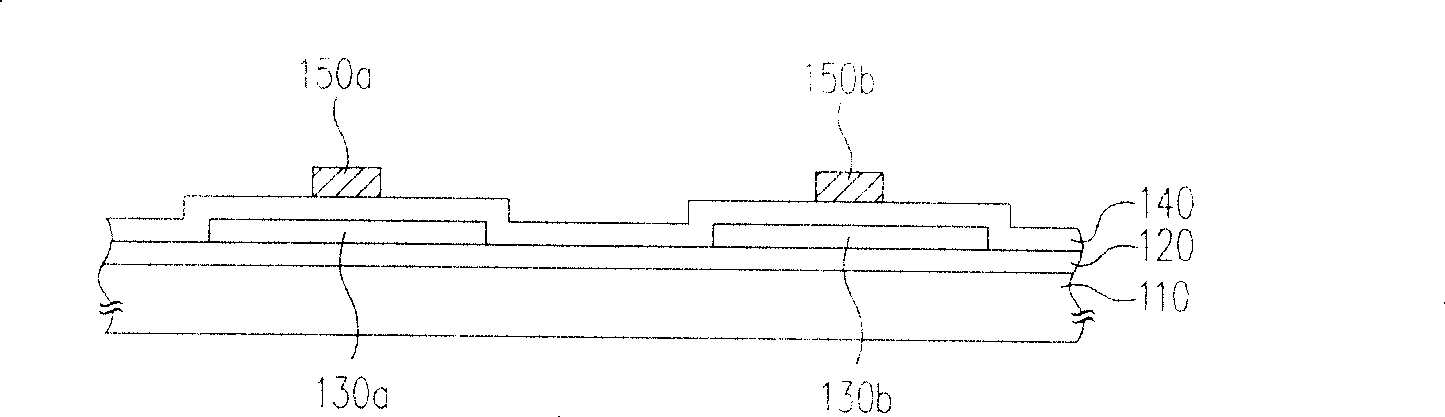

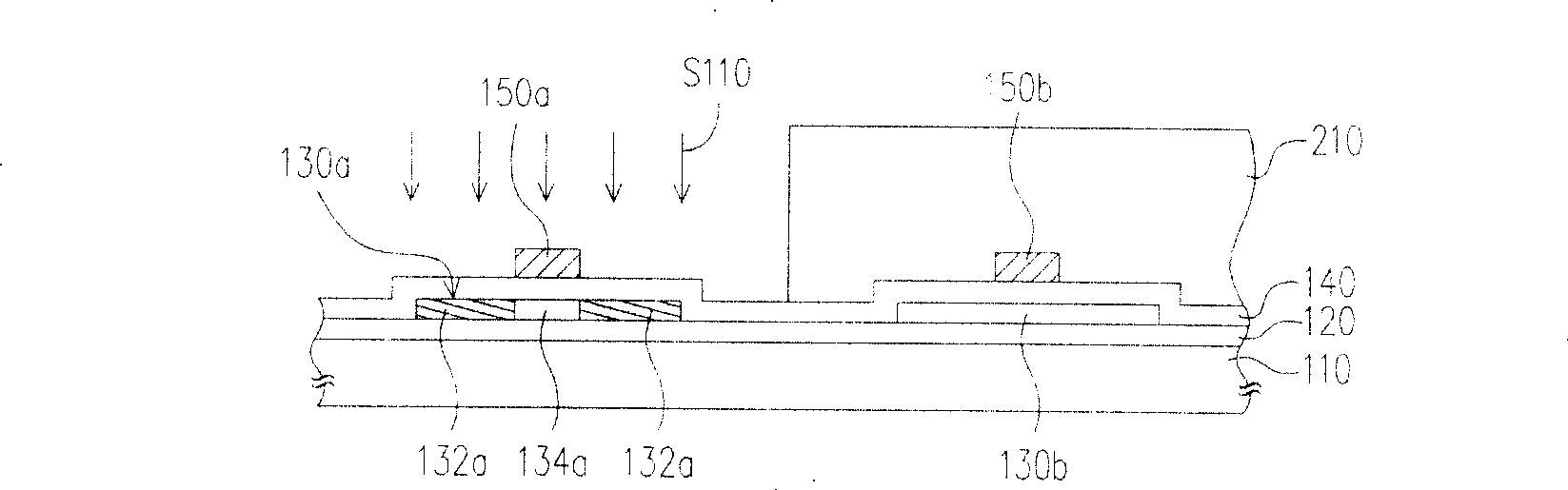

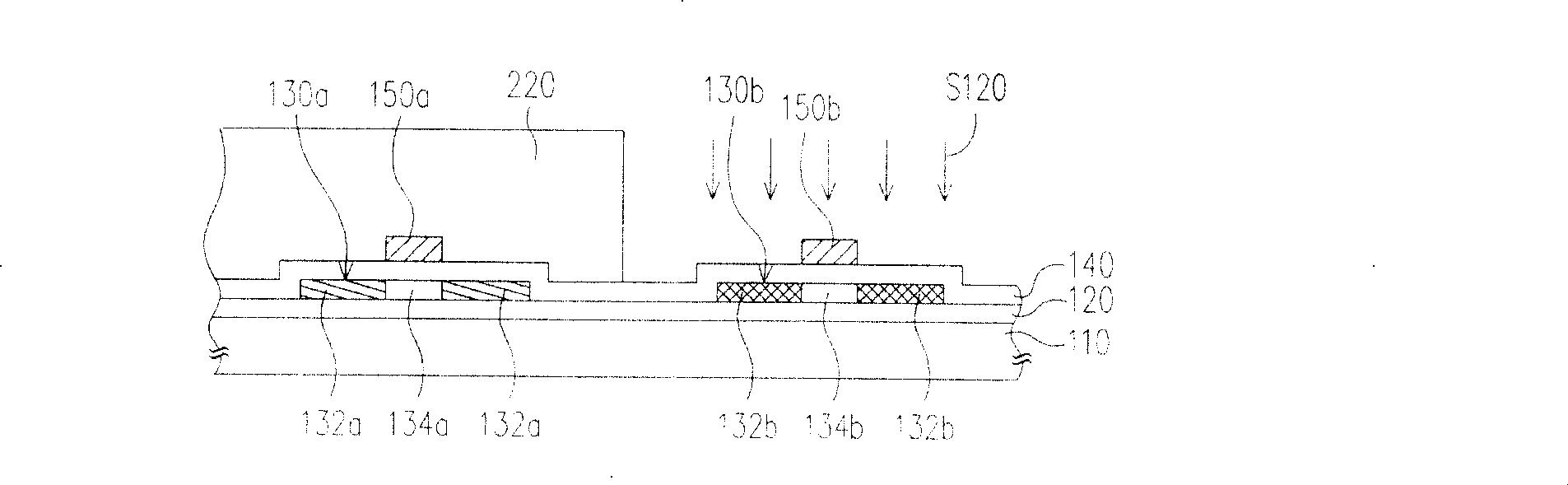

[0050] Figure 3A to Figure 3E It is a schematic diagram of the manufacturing method of the thin film transistor according to the first preferred embodiment of the present invention. Please refer to Figure 3A , The manufacturing method of the thin film transistor of this embodiment includes the following steps. First, a buffer layer 320 is formed on the substrate 310, wherein the buffer layer 320 may be formed by a low pressure chemical vapor deposition (low pressure CVD, LPCVD) process or a plasma enhanced chemical vapor deposition (plasma enhanced CVD, PECVD) process. In more detail, the buffer layer 320 is, for example, a single layer of silicon oxide or a double layer structure of silicon oxide / silicon nitride. In addition, the substrate 310 may be a glass substrate, a quartz substrate or a plastic substrate.

[0051] Then, a first polysilicon island 330 a and a second polysilicon island 330 b are formed on the buffer layer 320 . In more detail, the steps of forming t...

no. 2 example

[0066] Figure 4A to Figure 4F It is a schematic diagram of the manufacturing method of the thin film transistor according to the second preferred embodiment of the present invention. Please refer to Figure 4A , the second embodiment is similar to the first embodiment, the difference is that: after sequentially forming a buffer layer 320, a first polysilicon island 330a, a second polysilicon island 330b, a gate insulating layer 440, After the first gate 350a and the second gate 350b, use the first gate 350a and the second gate 350b as a mask to partially etch the gate insulating layer 440, so that the first gate 350a and the second gate 350b The thickness of the underlying gate insulating layer 440 is greater than the thickness of other parts of the gate insulating layer 440 . In more detail, the thickness of the etched gate insulating layer 440 is preferably 400 angstroms.

[0067] Figure 4B to Figure 4F steps with the previous Figure 3A to Figure 3E Similarly, it inc...

no. 3 example

[0071] Figure 5A to Figure 5E It is a schematic diagram of the manufacturing method of the thin film transistor according to the third preferred embodiment of the present invention. Please refer to Figure 5A , the third embodiment is similar to the first embodiment, the difference is that: after sequentially forming the buffer layer 320, the first polysilicon island 330a, the second polysilicon island 330b, the gate insulating layer 540, After the first gate 350a and the second gate 350b, use the first gate 350a and the second gate 350b as a mask to completely etch the gate insulating layer 540 not covered by the first gate 350a and the second gate 350b .

[0072] Figure 5B to Figure 5E The steps are also the same as the previous Figure 3B to Figure 3E Similarly, it includes forming the sacrificial layer 360, forming the photoresist layer 610, removing part of the sacrificial layer 360, forming the first source / drain 532a and the first channel region 534a between the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More