Circuit capable of eliminating NMOS single tube transmission to form static short circuit current

A short-circuit current and circuit technology, applied in the direction of logic circuit coupling/interface, logic circuit connection/interface layout using field effect transistors, etc., can solve the problem of large circuit area consumption, exceeding noise tolerance, weakening the signal strength when transmitting high level and other problems, to achieve the effect of simple design steps, saving chip area, and avoiding static short-circuit current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

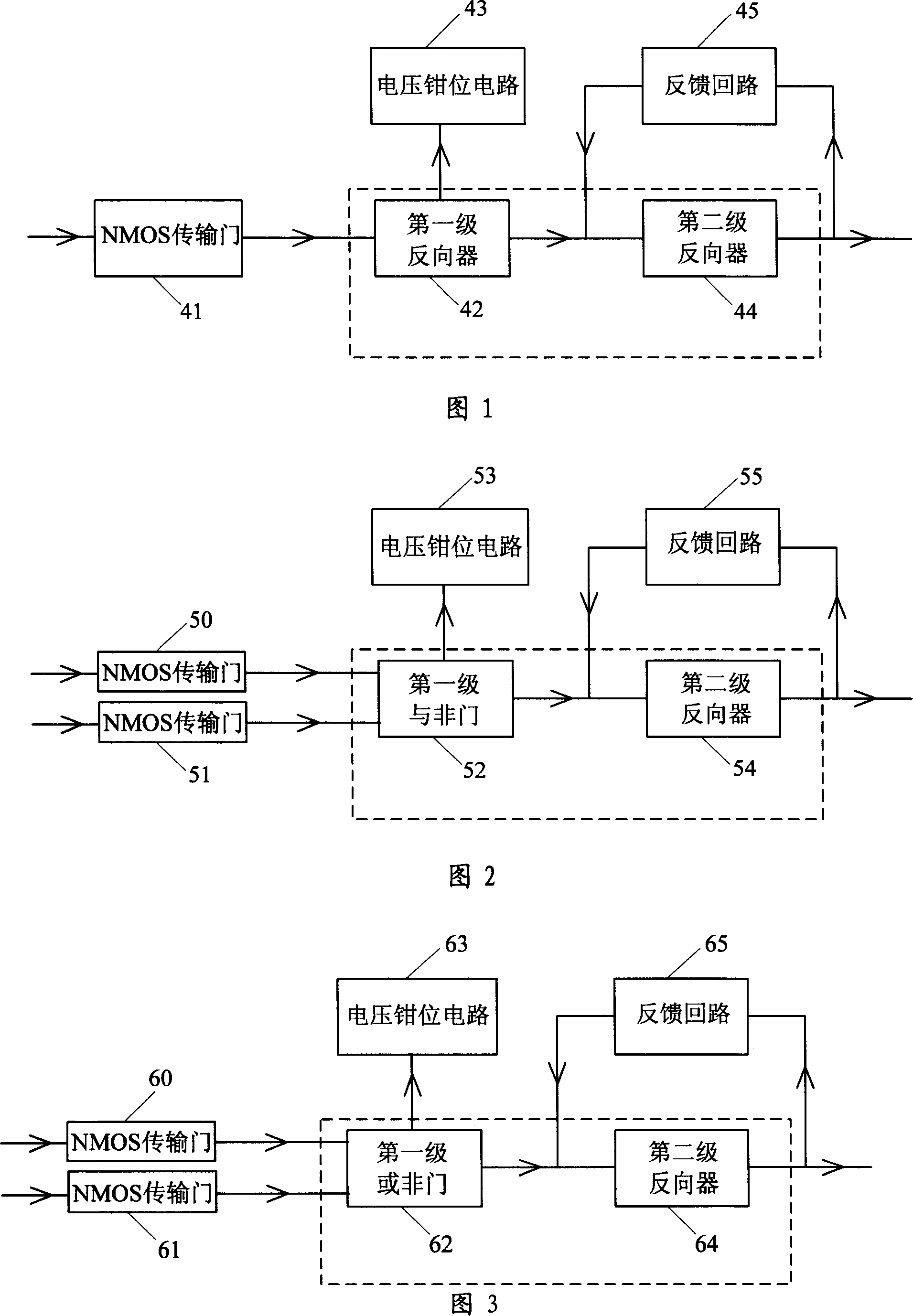

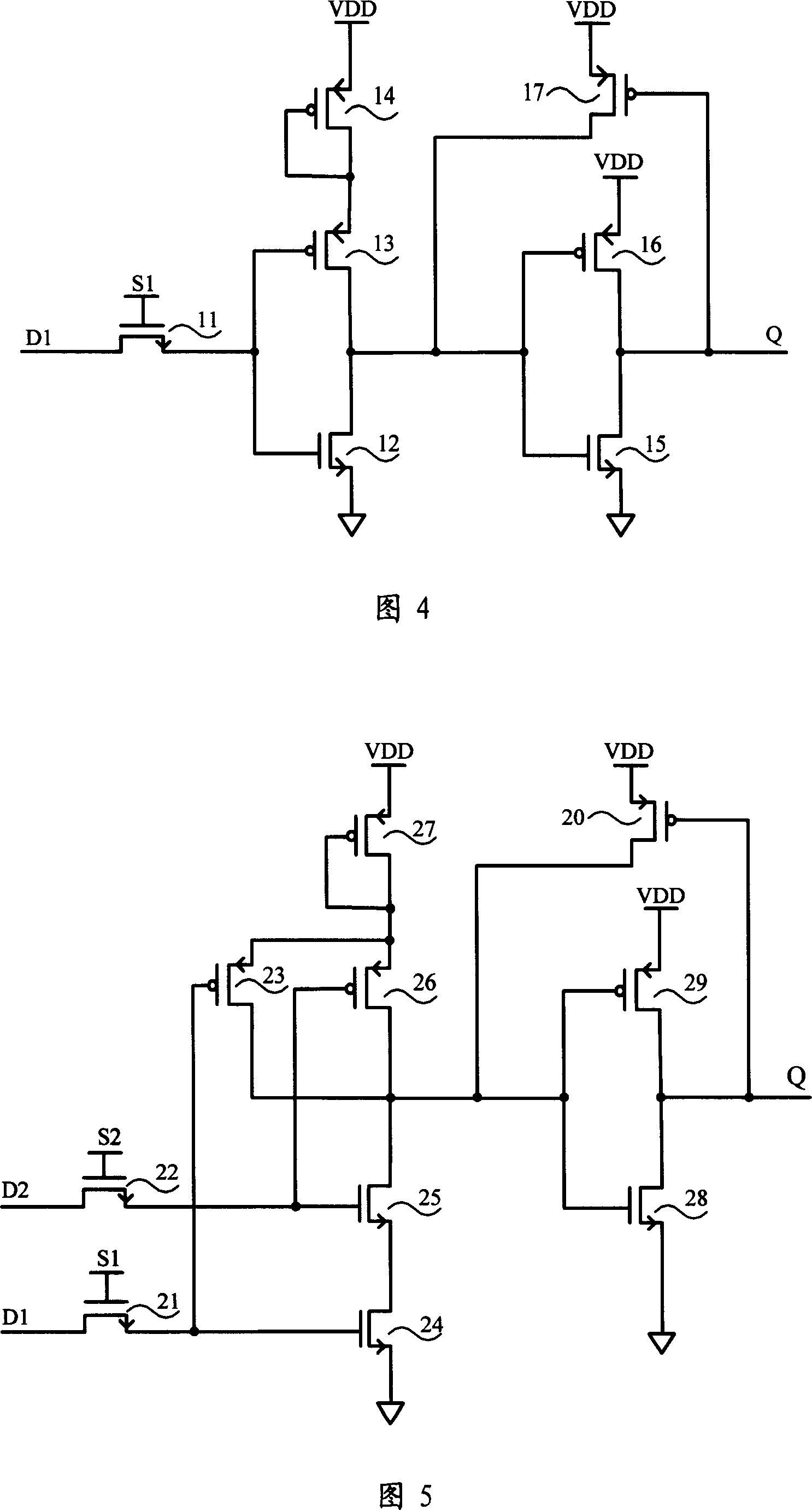

[0026] As shown in FIG. 1 and FIG. 4 , the NMOS transmission gate 41 is composed of the NMOS transmission transistor 11 , the voltage clamping circuit 43 is composed of the PMOS transistor 14 , and the feedback loop 45 is composed of the PMOS transistor 17 . When D1=1 (power supply voltage VDD), the NMOS transmission tube 11 is turned on through the control signal S1, and a high level VDD-V with a threshold drop is output th , the NMOS transistor 12 is turned on, and the source voltage of the PMOS transistor 13 is clamped at VDD-V by the PMOS transistor 14 th , so the source-gate voltage difference of the PMOS transistor 13 is less than the threshold voltage, the PMOS transistor 13 is guaranteed to be cut off, and the static short-circuit current generation is avoided at this stage; the first-stage inverter 42 outputs a low level, and the second-stage inverter In 44, the NMOS transistor 15 is turned off, the PMOS transistor 16 is turned on, the second-stage inverter 44 outputs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More