Semiconductor package and its array arranged substrate structure and production method

An array arrangement, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of uneven cutting surface, burning cutting surface, irregular shape, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

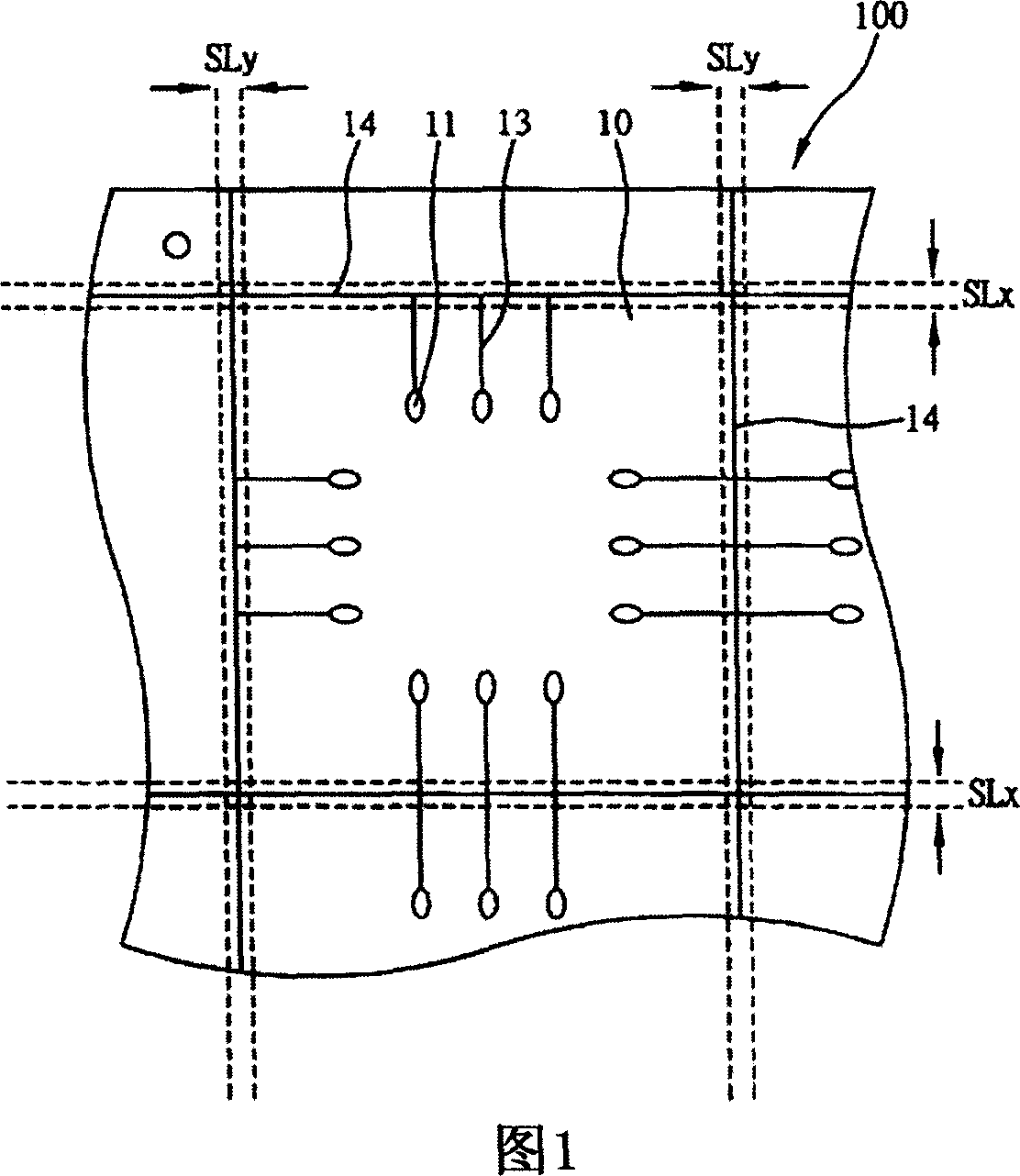

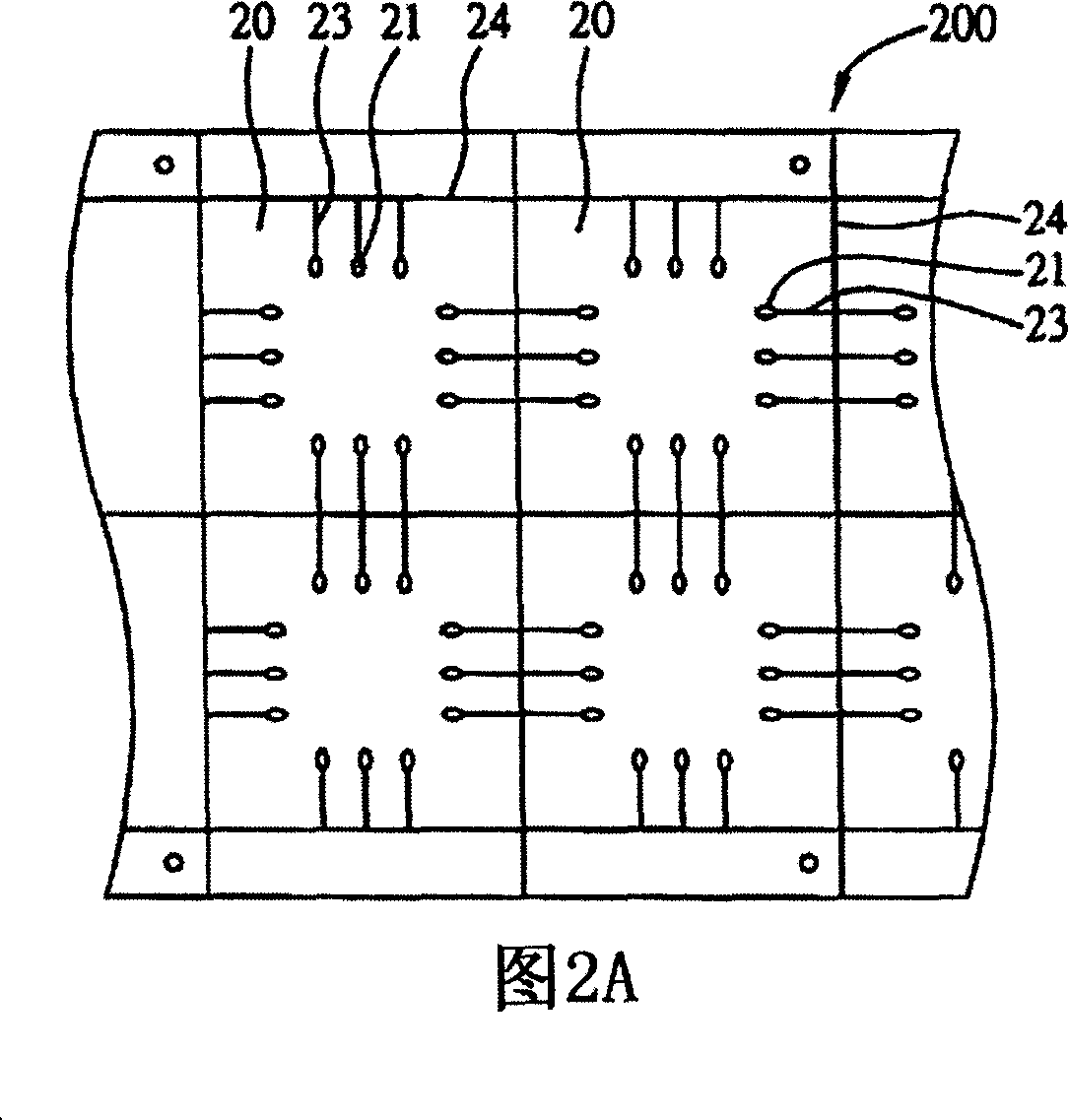

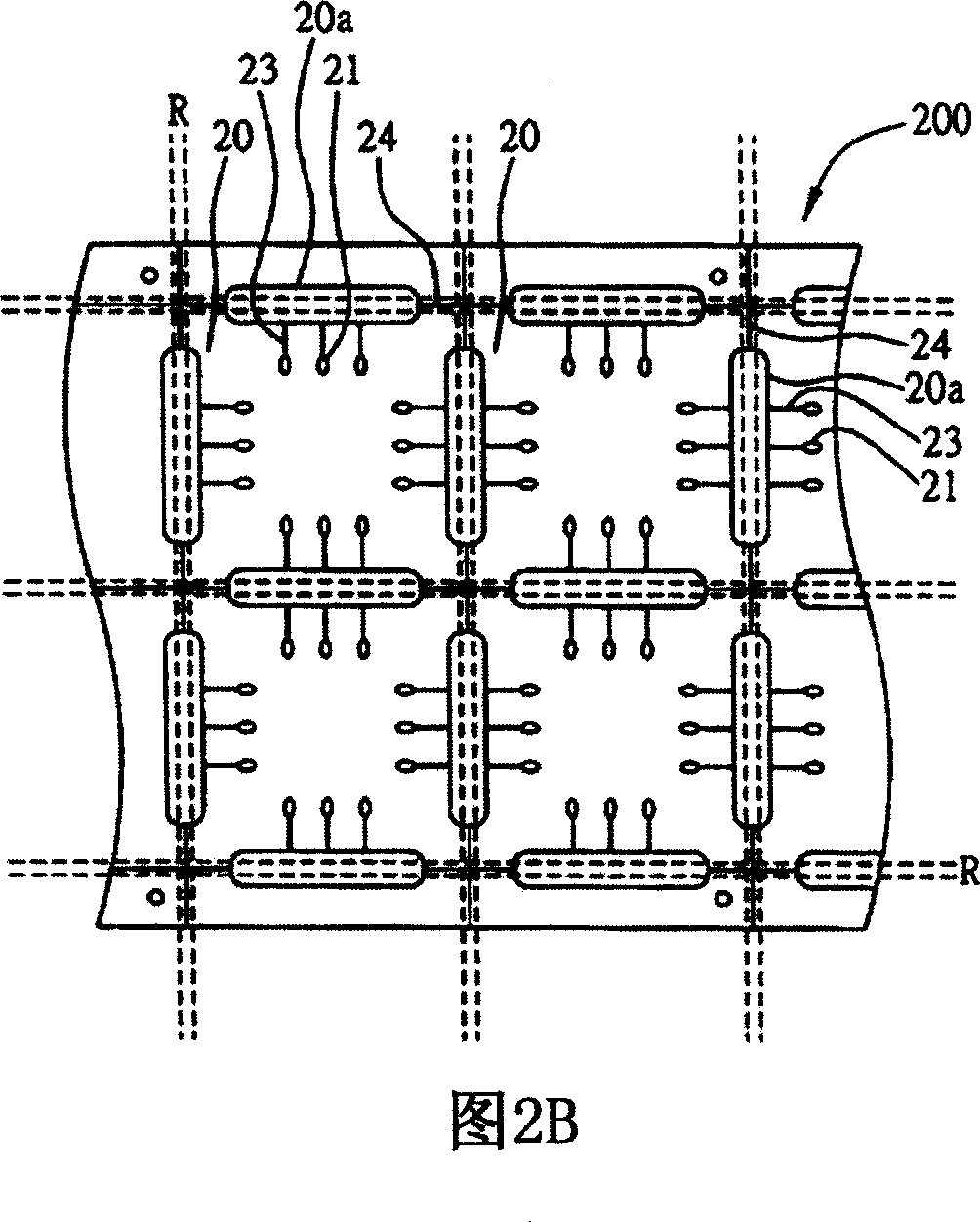

[0031] 2A to 2F are schematic diagrams of Embodiment 1 of the semiconductor package and its array-arranged substrate structure and manufacturing method of the present invention. The semiconductor package may be a thin profile ball grid array (TFBGA) semiconductor package.

[0032] The manufacturing method of the semiconductor package of the present invention is shown in FIG. 2A. First, a substrate 200 is provided, and the substrate sheet 200 includes: a plurality of substrate units 20 arranged in an array, with An electroplating bus 24, and an electrical connection pad 21 is provided in the substrate unit 20, and a conductive circuit 23 electrically connecting the electrical connection pad 21 and the electroplating bus 24, through the electroplating bus 24 and the conductive circuit 23, in An electroplated metal layer (not shown) such as nickel / gold is formed on the electrical connection pad 21 , wherein the electrical connection pad 21 is used for electrical connection betwee...

Embodiment 2

[0039] 3A to 3D are schematic diagrams of Embodiment 2 of the semiconductor package and its manufacturing method of the present invention.

[0040] As shown in Fig. 3A, a substrate 300 is provided, and the substrate 300 includes: a plurality of substrate units 30 arranged in an array, an electroplating bus 34 is provided between the substrate units 30, and in the substrate units 30 An electrical connection pad 31 and a conductive circuit 33 electrically connecting the electrical connection pad 31 and the electroplating bus 34 are provided, and an electroplated metal layer (not shown) is formed on the electrical connection pad 31 through the electroplating bus 34 and the conductive circuit 33. marked).

[0041] As shown in FIG. 3B , slots 30 a are formed between each of the substrate units 30 , and the slots 30 a cut off the connection relationship between the conductive lines 33 and the electroplating bus 34 . The width of the slot 20 a is greater than the width of a dicing l...

Embodiment 3

[0046] 4A to 4B are schematic diagrams of Embodiment 3 of the semiconductor package and its manufacturing method of the present invention. This embodiment is substantially the same as the above-mentioned embodiments, the main difference is that: the semiconductor package and its manufacturing method are applied to the memory card package.

[0047] As shown in Figure 4A, a substrate 400 is provided, and the substrate 400 includes: a plurality of substrate units 40 arranged in an array, each of the substrate units 40 is used to establish a Micro SD memory card package, the substrate unit 40 An electroplating bus 44 is provided between them, and an electrical connection pad 41 is provided in the substrate unit 40, and a conductive circuit 43 electrically connecting the electrical connection pad 41 and the electroplating bus 44 passes through the electroplating bus 44 and conducts electricity. The circuit 43 forms an electroplated metal layer (not shown) on the electrical connecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More