High voltage MOS transistor circuit simulated macro model

A technology of MOS transistors and simulation models, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as lack of physical meaning, complex extraction process, and high difficulty, so as to achieve convenient and fast extraction of parameters and model simulation Accurate and portable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The high-voltage MOS transistor circuit simulation macro model of the present invention will be further described in detail below.

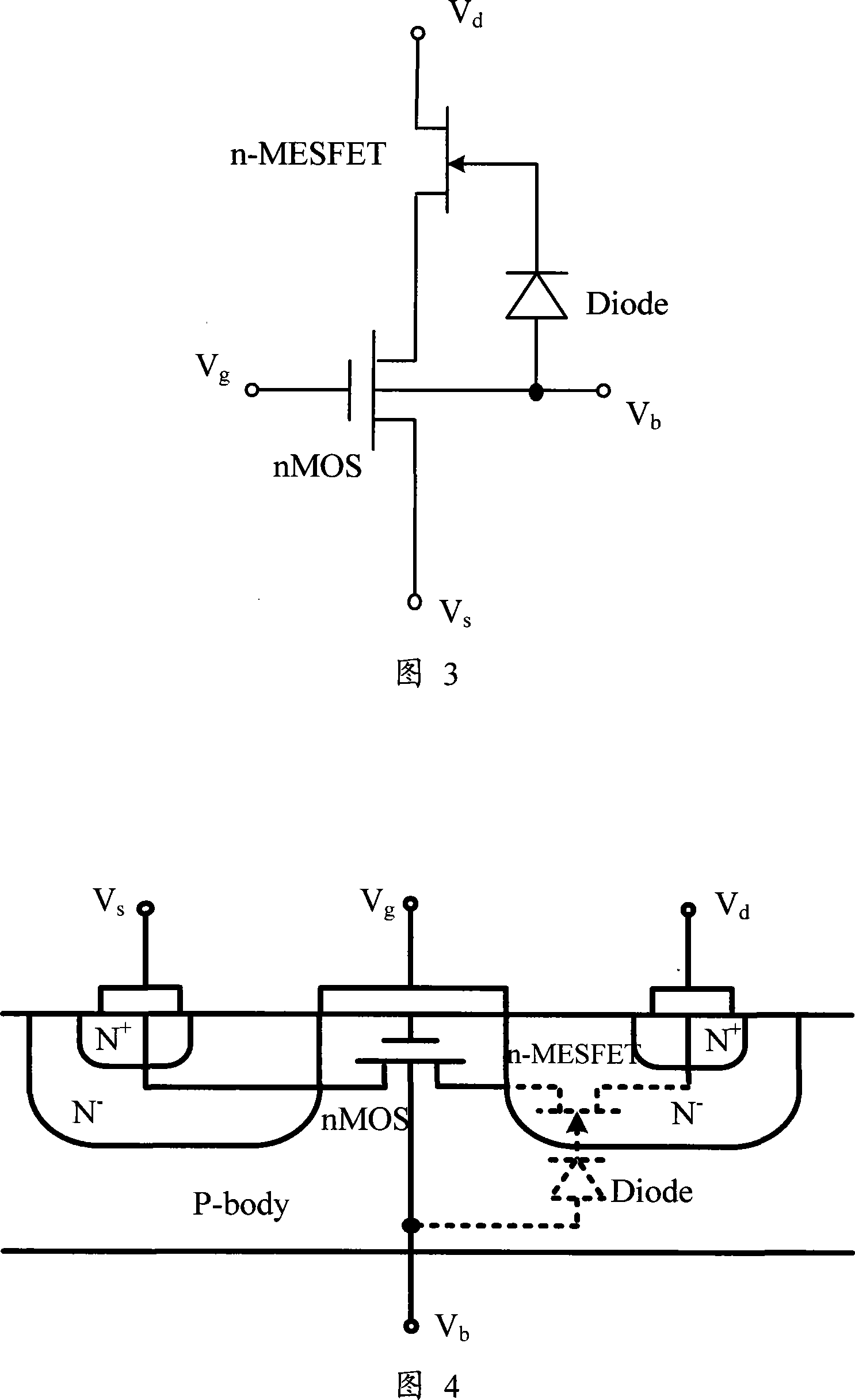

[0031] As shown in Figure 3, the high-voltage MOS transistor circuit emulation macro model of the present invention comprises a MOS transistor emulation model nMOS, an n-channel JFET emulation model n-MESFET and a diode emulation model Diode, and its specific circuit connection mode is: in nMOS The n-MESFET is connected in series on the drain of the nMOS, and the Diode is connected in series between the drain and the gate of the nMOS. The variable resistance characteristic of JFET is used to simulate the lightly doped drain diffusion region of the high-voltage MOS transistor, and the diode is used to simulate the equivalent PN junction between the substrate and the N-type drain.

[0032] Figure 4 is a schematic diagram of the structure of a high-voltage MOS transistor. The position of each circuit component (nMOS, n-MESFET, Diode) of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More