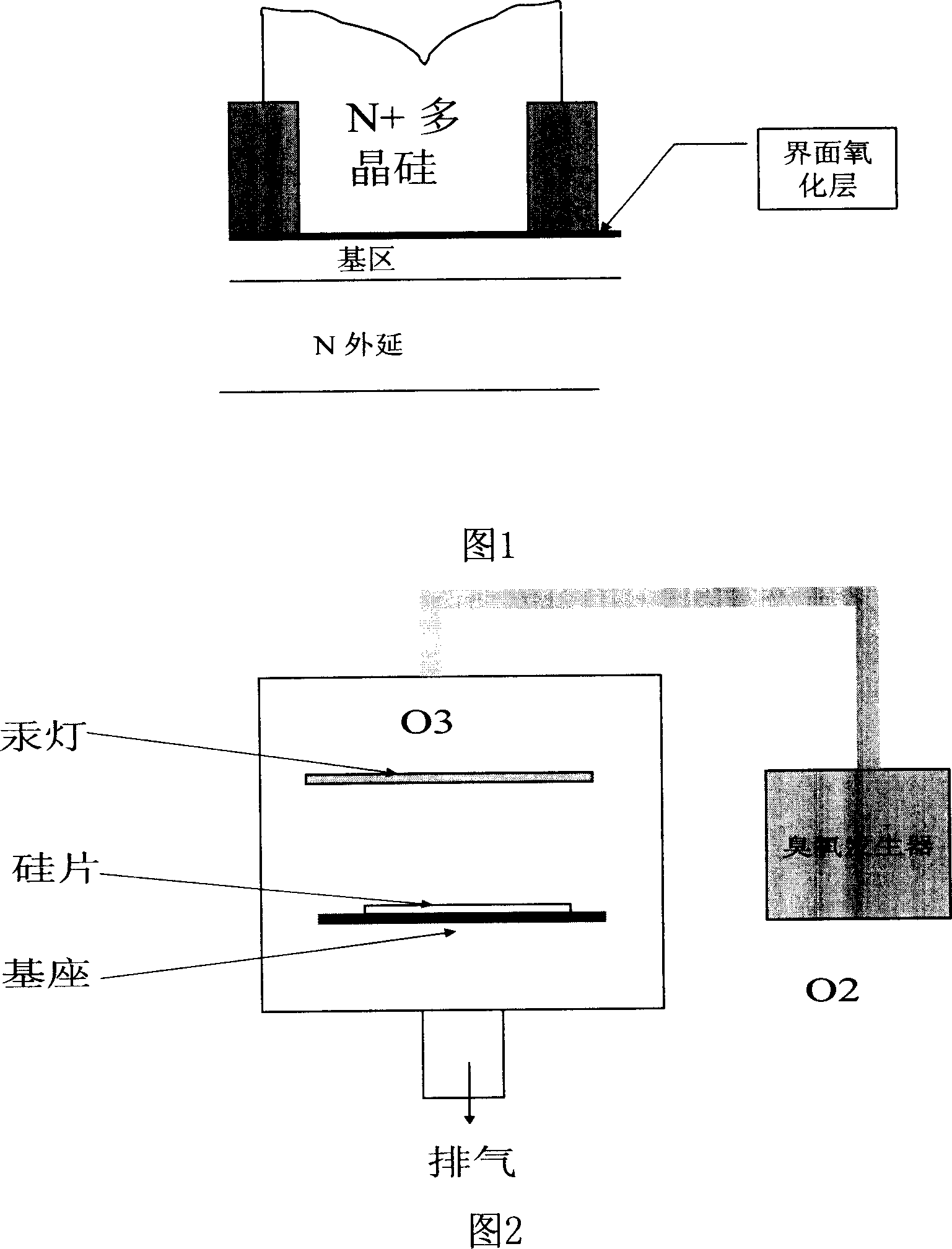

Method for manufacturing polycrystalline silicon emitter interface layer

An emitter and interface layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of poor uniformity of silicon wafers and the oxide layer is not very dense, and achieve easy temperature control, rapid quality, Simple process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

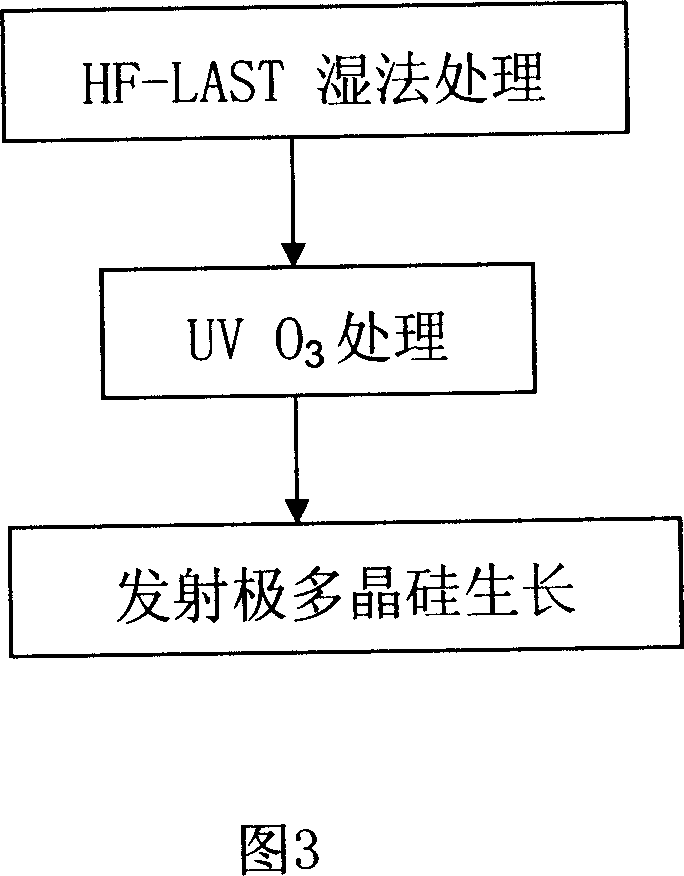

Embodiment 1

[0018] In this example, firstly, the surface of the silicon wafer is cleaned by HF-Last wet method according to the method of the present invention to ensure that the natural oxide layer on the surface is completely removed, and then the silicon wafer is placed into the UV O process as shown in Figure 2. 3 In the schematic diagram of the treatment device; the introduction of oxygen as shown in Figure 2 UV O 3 processing device, the UV O 3 The ozone generator of the processing device processes oxygen to generate ozone, and the mercury lamp of the processing device heats up; in this embodiment, the temperature in the processing device is controlled at: 150-250 degrees Celsius and the processing time is 8 minutes; the Bipolar polysilicon emitter interface is made by this example The oxide layer is relatively uniform and of good quality, and the thickness of the oxide layer formed in this example is 10 angstroms. The polysilicon emitter interface layer of BiCMOS can also be made ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More