Interleaved three-dimensional on-chip differential inductors and transformers

A three-dimensional chip, interleaved technology, applied in variable inductor/transformer, inductor/transformer/magnet manufacturing, inductors, etc., can solve problems such as limiting the self-resonant frequency of on-chip inductors and transformers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

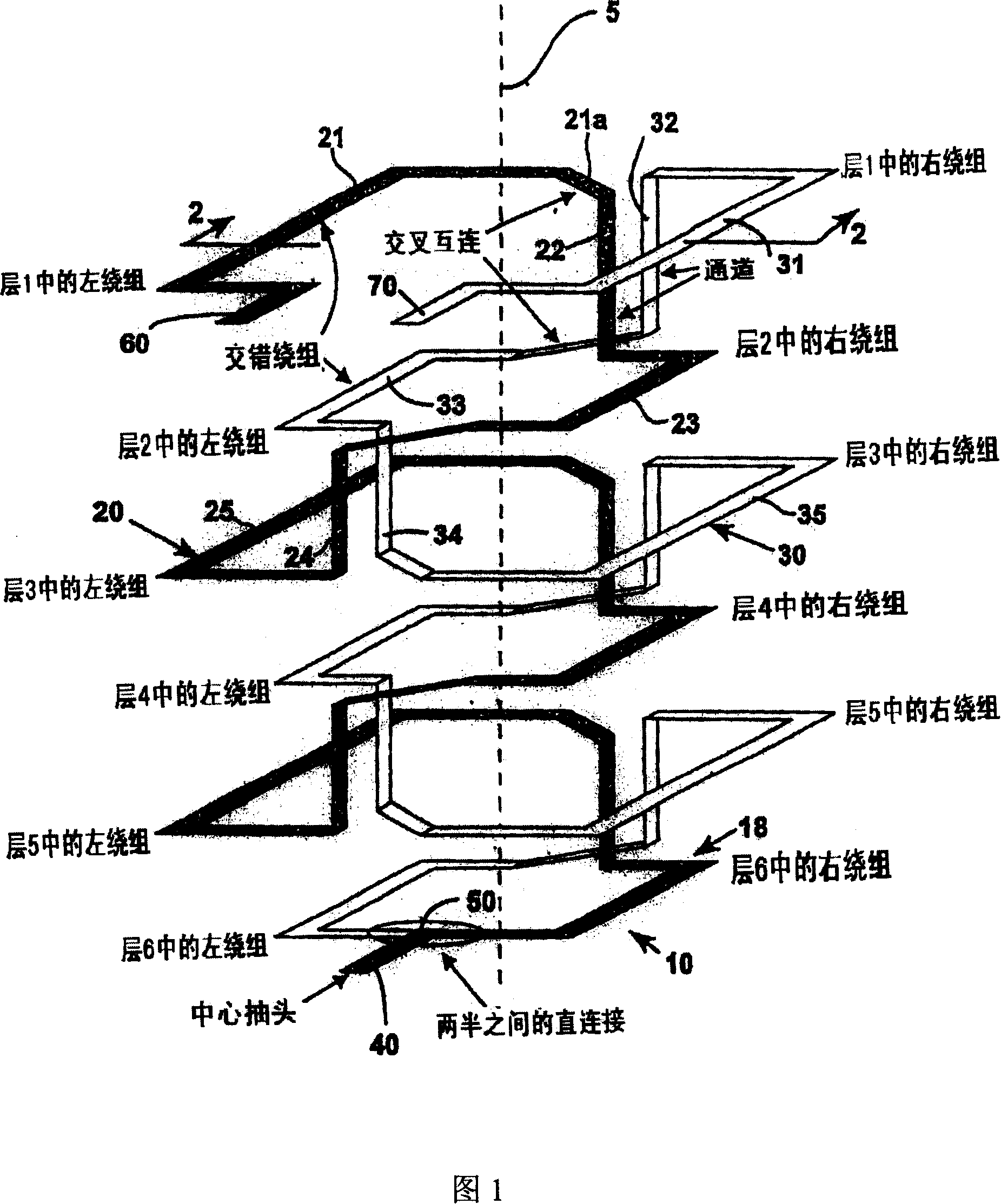

[0037] Various interleaved 3D on-chip differential inductors and transformers are provided according to the present invention.

[0038]The interleaved 3D on-chip differential inductors and interleaved on-chip transformers are well known to those skilled in the art such as complementary metal oxide semiconductor (CMOS), bipolar transistor and integration of CMOS technologies (BiCMOS), and Manufactured with standard processes in silicon-germanium (SiGe) technology.

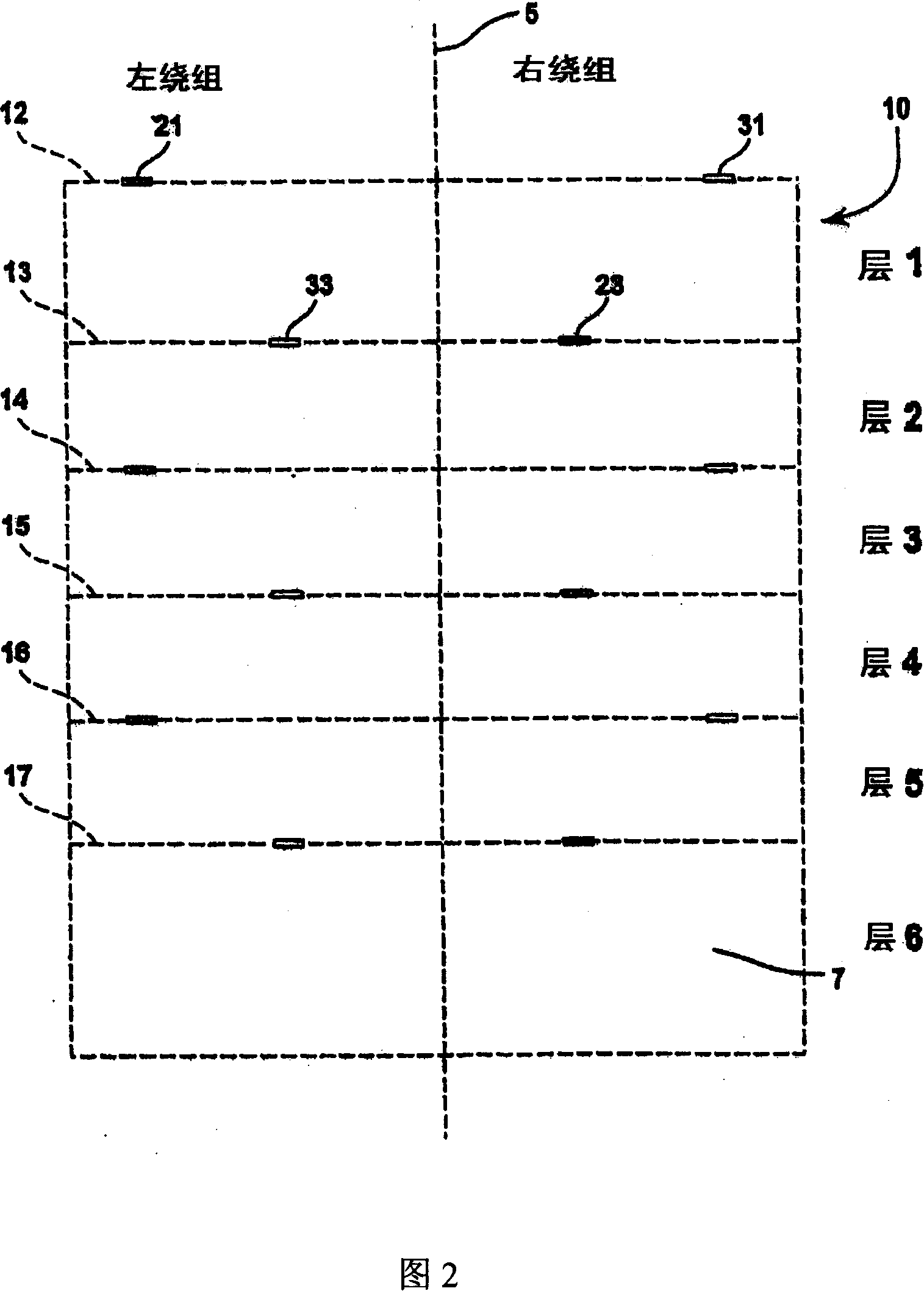

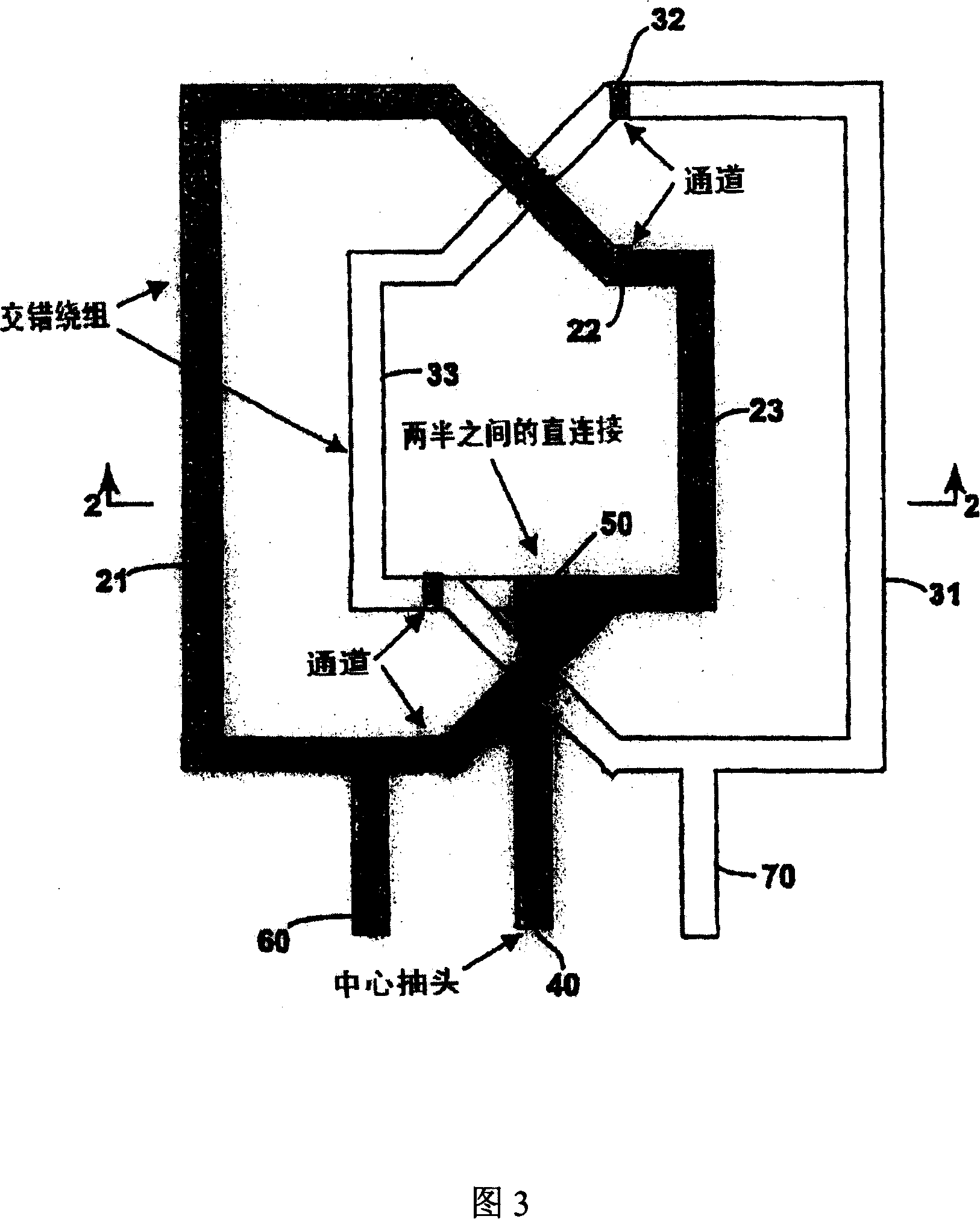

[0039] The interleaved 3D on-chip differential inductors and interleaved on-chip transformers described below were fabricated as multiple layers comprising windings. The layers of the winding are patterned, deposited or otherwise disposed on the layers as they are created. The windings between the layers are interconnected by vias.

[0040] FIG. 1 shows a perspective view of a preferred embodiment of an interleaved on-chip differential inductor, generally designated reference numeral 10 . 2 and 3 respectively sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com