Junction field effect tube and method of manufacturing the same

A field effect transistor and a manufacturing method technology, applied in the field of junction field effect transistor and its manufacturing, can solve problems such as voltage resistance deterioration, and achieve the effects of low cost, increased area, and reduced impurity concentration difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

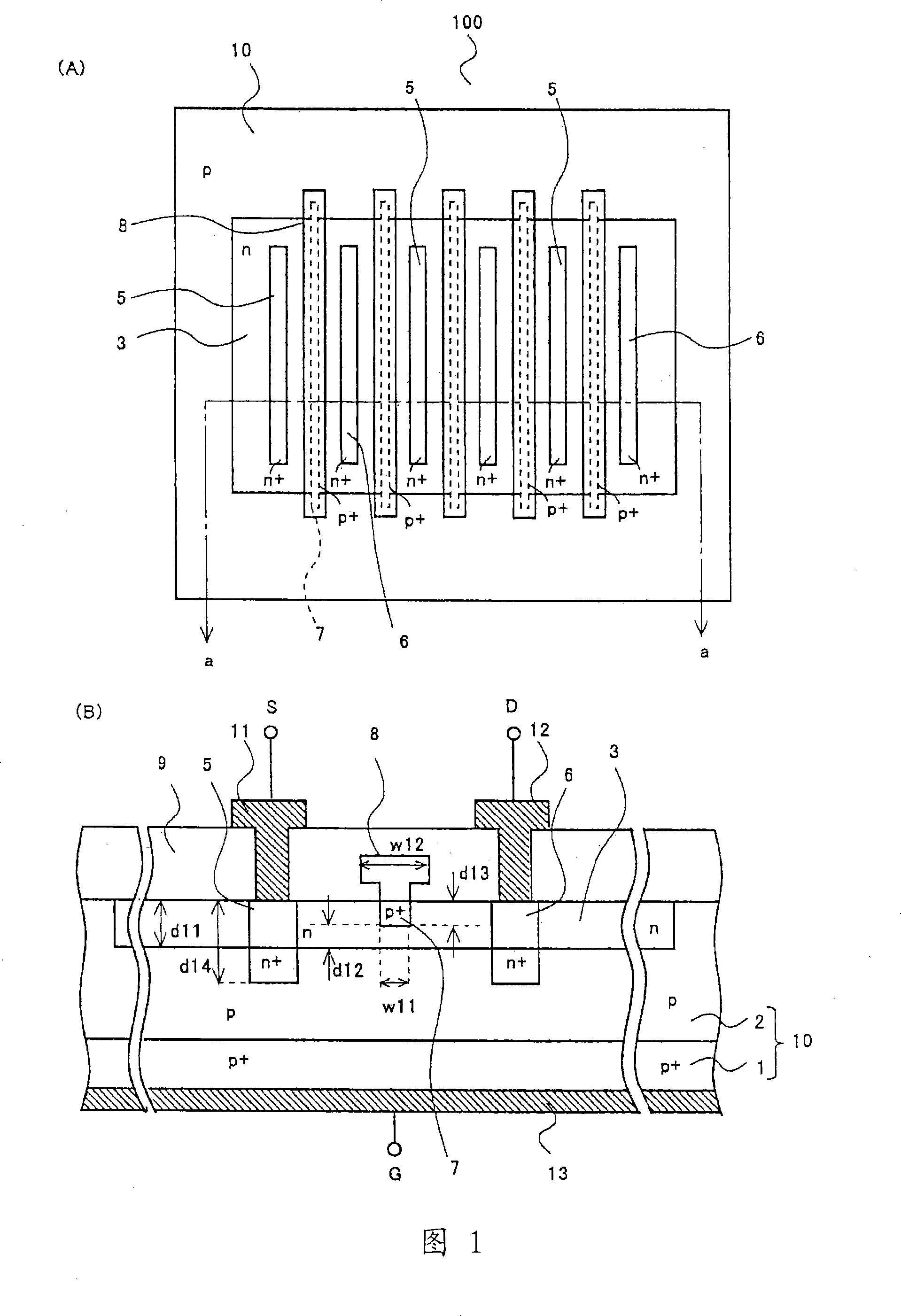

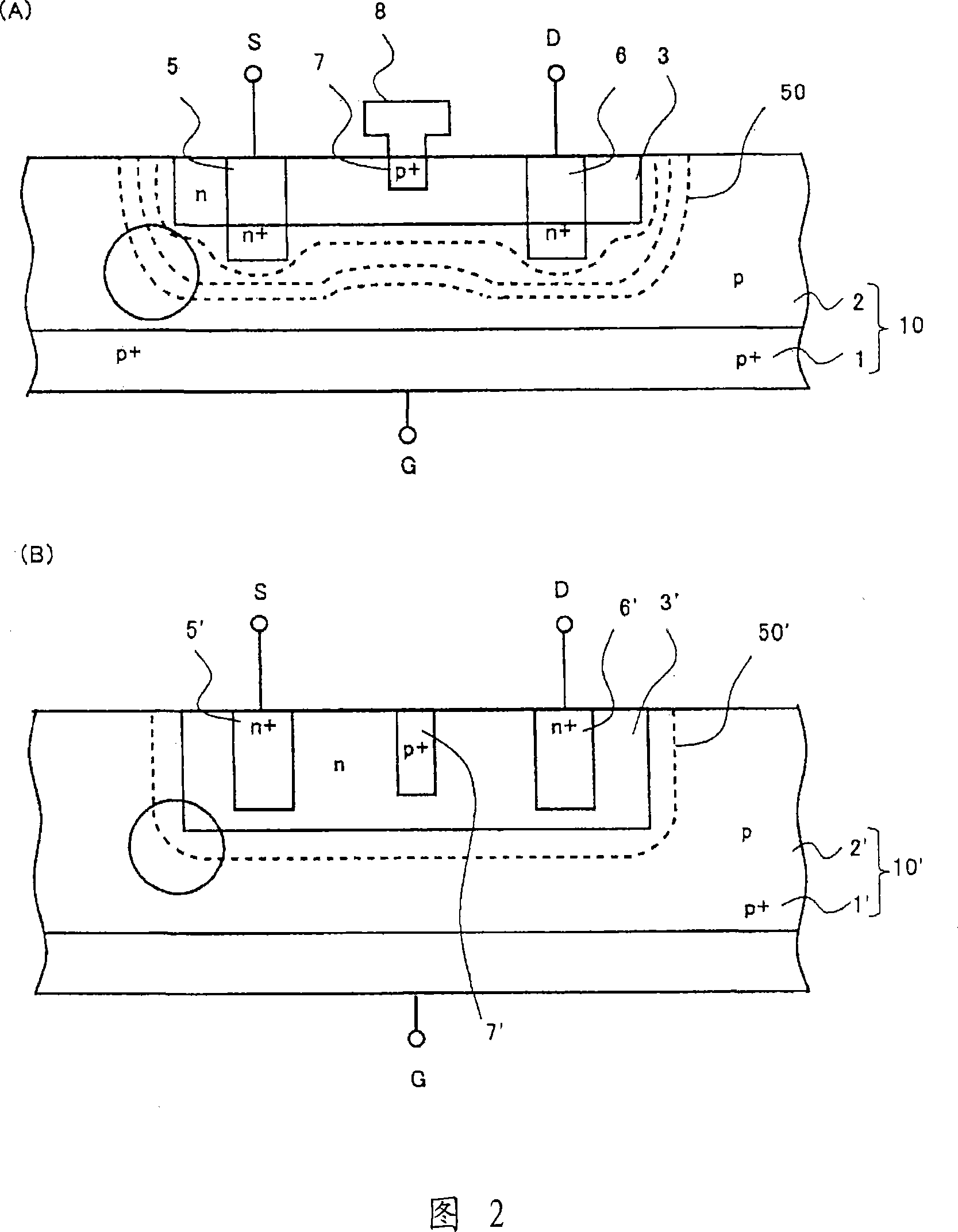

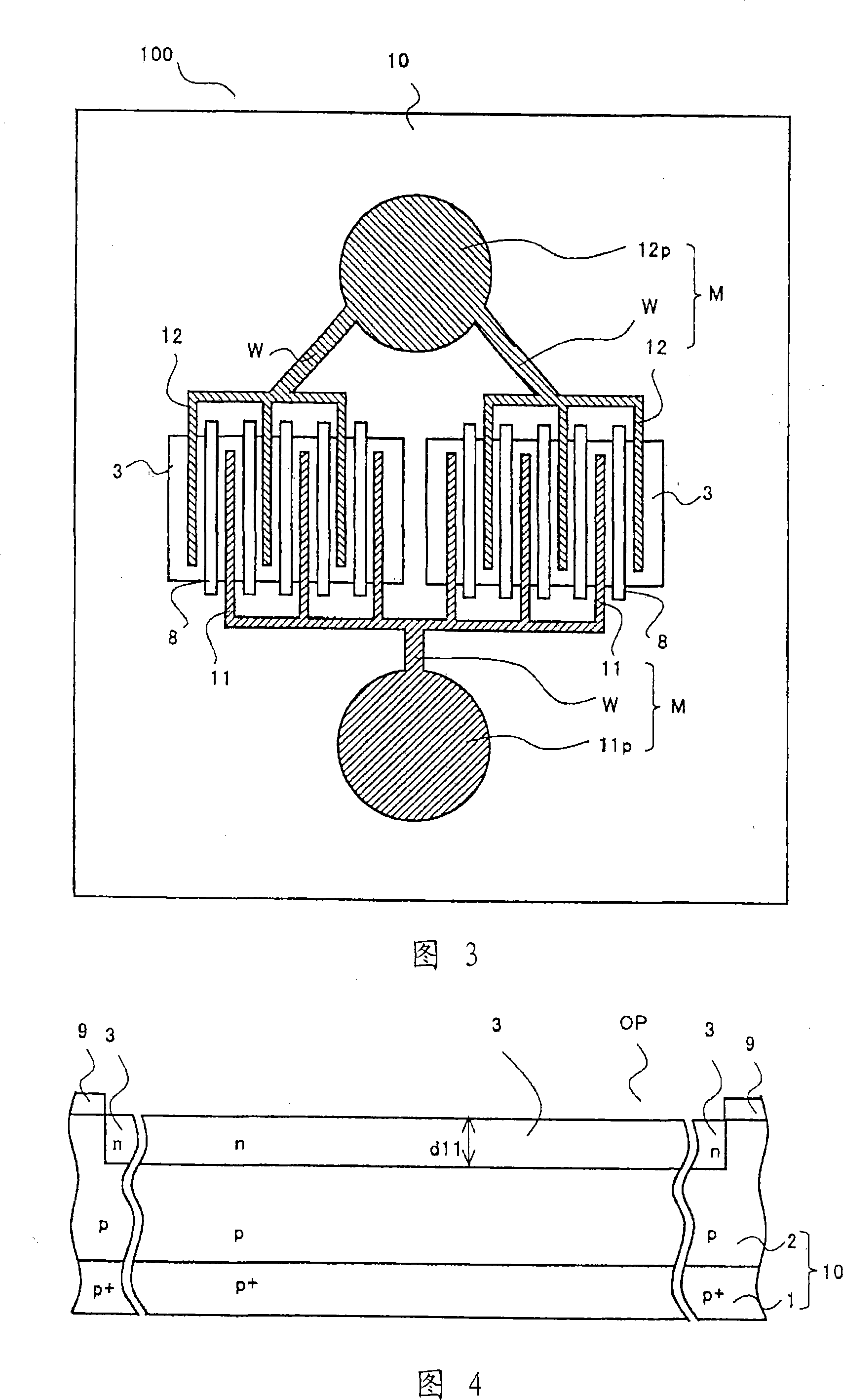

[0073] The junction field effect transistor of the present invention will be described in detail with reference to FIGS. 1 to 8 .

[0074] FIG. 1 is a diagram showing a junction field effect transistor 100 of this embodiment. FIG. 1(A) is a plan view, and FIG. 1(B) is a partial sectional view taken along line a-a of FIG. 1(A). In addition, in FIG. 1(A), the insulating film and metal electrodes (source electrode and drain electrode) on the surface of the substrate are omitted. In addition, FIG. 1(B) shows one cell represented by a set of source region, drain region, and gate region.

[0075] The junction field effect transistor 100 of the present invention is composed of a semiconductor substrate 1 , a semiconductor layer 2 , a channel region 3 , a source region 5 , a drain region 6 , a gate region 7 , and a conductive layer 8 .

[0076] Referring to FIG. 1(A), an n-type channel region 3 is provided on the surface of a p-type semiconductor substrate 10 . On the surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More