Encryption-decryption coprocessor for SOC, implementing method and programming model thereof

A coprocessor, encryption and decryption technology, applied in the field of ultra-large-scale digital integrated circuits, can solve the problems of increased power consumption and chip area, and achieve the effect of low power consumption and small hardware scale

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

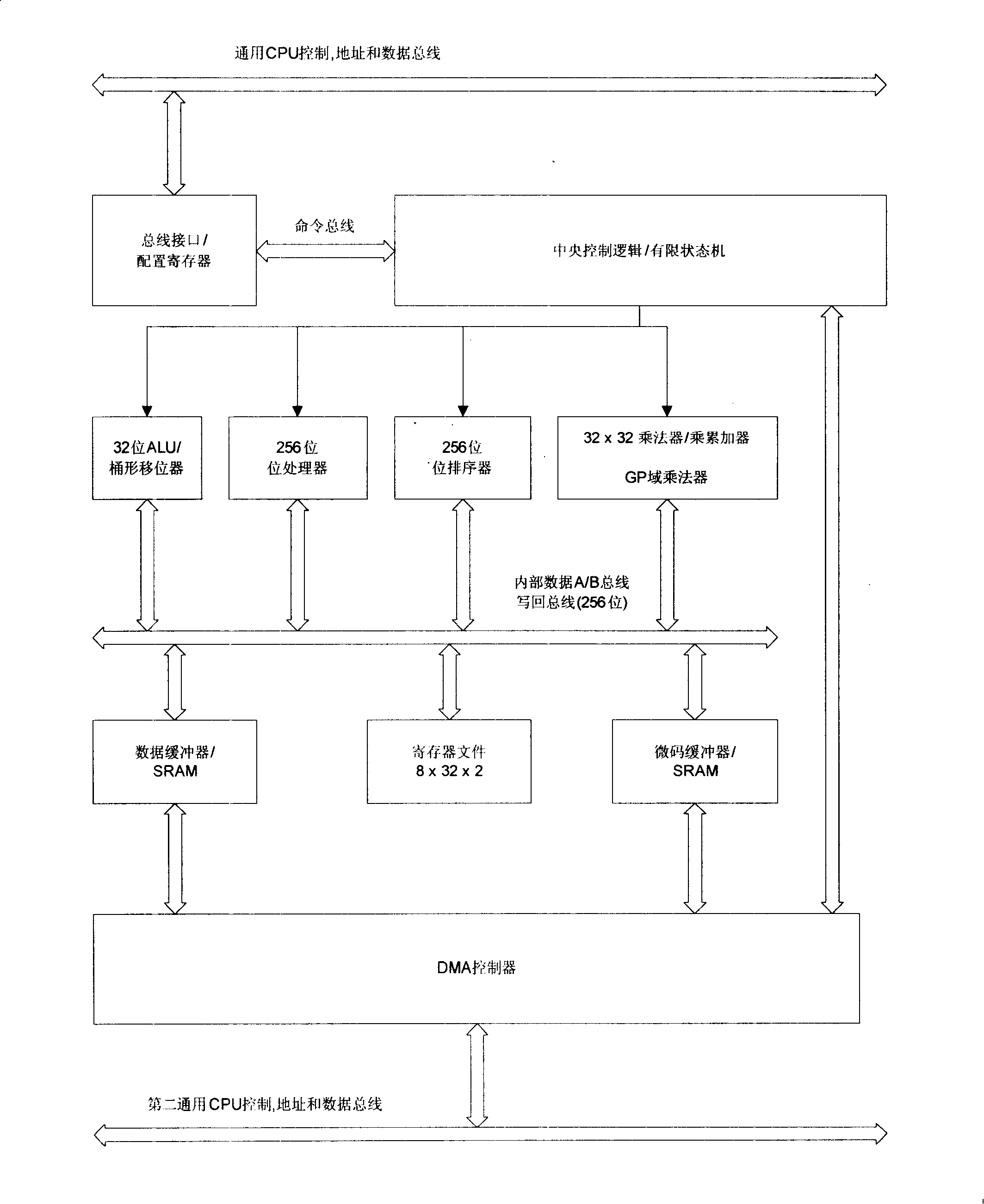

[0033] As shown in the figure, the encryption and decryption coprocessor applicable to SOC design of the present invention includes a bus interface and a configuration register, a central control module, a 32-bit ALU (operator) and a barrel shifter, a 256-bit processor, a 256 Bit sorter, 32-bit multiply, multiply accumulate and field multiplier, internal bus, data buffer, register file, DMA (direct data transfer) controller.

[0034] The bus interface (that is, the coprocessor interface) and the configuration register are connected to a general-purpose CPU (central processing unit) bus. The general-purpose CPU bus includes a 32-bit data input bus, a 32-bit data output bus, and a 32-bit address bus. Control signals include CS (chip select), RW (read and write), INT (interrupt) and SEL (data granularity). The general-purpose CPU bus can be easily connected with various popular CPU bus architectures, such as AHB and APB of ARM, WISHBONE of OpenCore and OPB of IBM, etc.

[0035] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More