Flush type capacitance ultra-low inductance design

A technology of capacitors and capacitors, which is applied in the field of ultra-low parasitic inductance design, can solve the problems of reducing magnetism and reducing parasitic inductance of embedded capacitors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

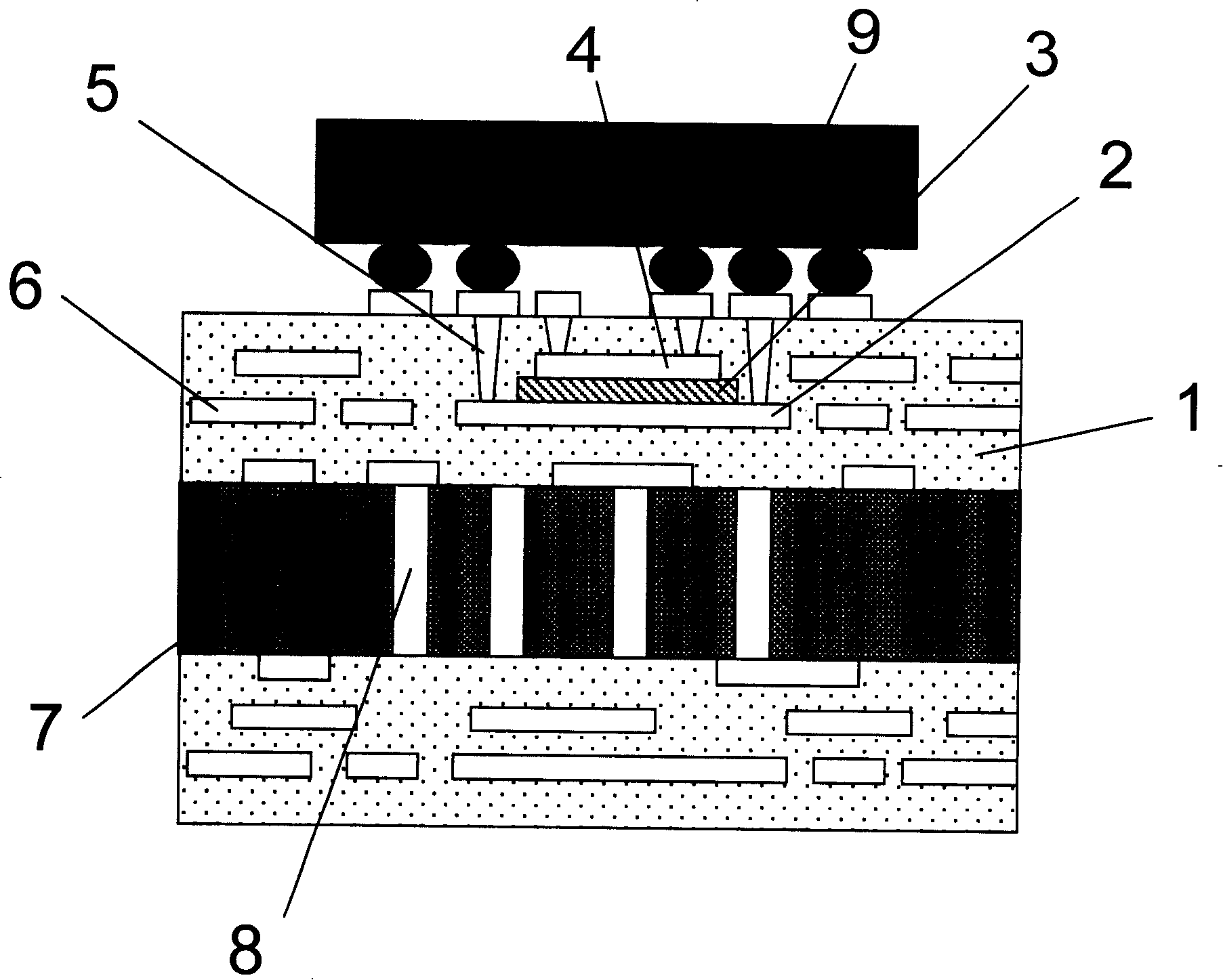

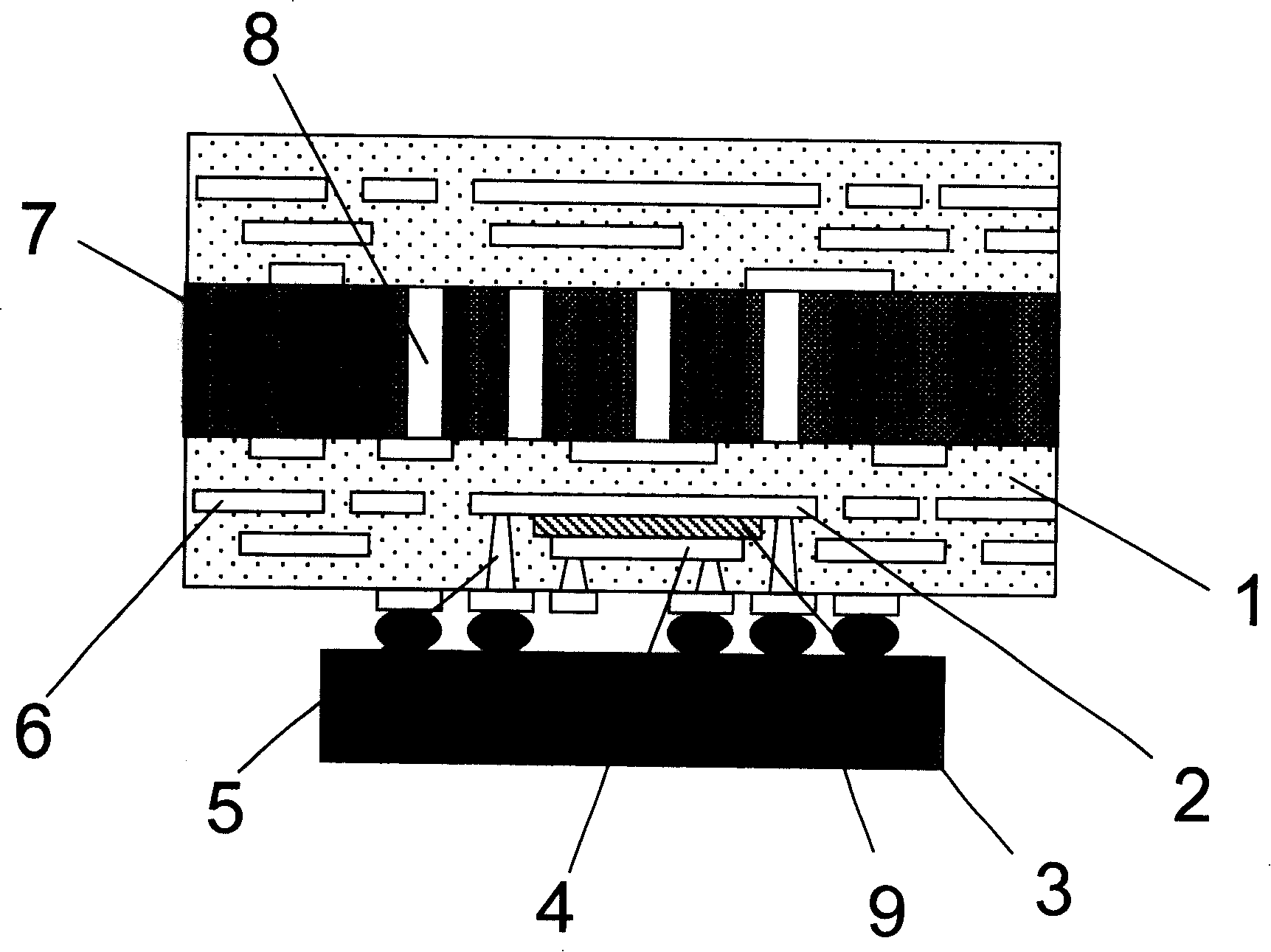

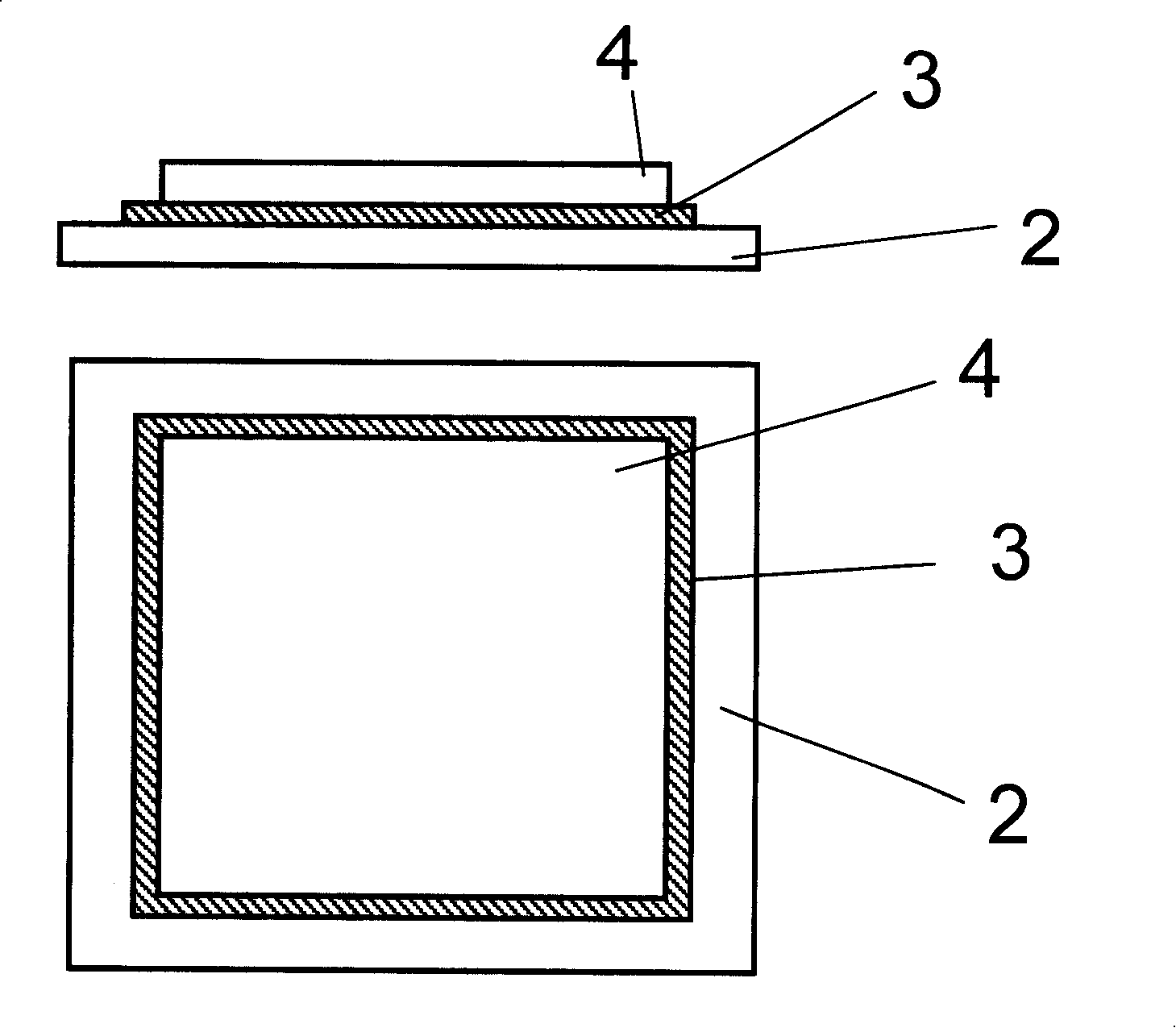

Image

Examples

Embodiment Construction

[0036] 1. The target impedance and upper limit frequency of the power supply network are determined by the technical parameters of the integrated circuit

[0037] Target impedance = power supply voltage × allowable fluctuation percentage / maximum transient current

[0038] Generally, the allowable fluctuation percentage is 5% to 10%, depending on the specific conditions of the system. The impedance of the system power supply network shall not be greater than this target impedance within the specified frequency range. The specified frequency range is generally from DC to the upper frequency limit. The upper limit frequency is generally defined as half the frequency of the rising edge of the signal. For example, a signal whose rising edge is 1 nanosecond has an upper limit frequency of 500MHz.

[0039] 2. Determine the reference capacitance

[0040] Only high frequency decoupling capacitors are estimated here. A reference capacitance value is determined by the upper freque...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More