Method for manufacturing a leadframe, packaging method for semiconductor element and semiconductor package product

A lead frame and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of long product delivery, high cost, and difficulty in reducing power consumption of radio frequency and analog circuits. Achieve the effect of shortening the signal path, saving lead pins, and improving electronic characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

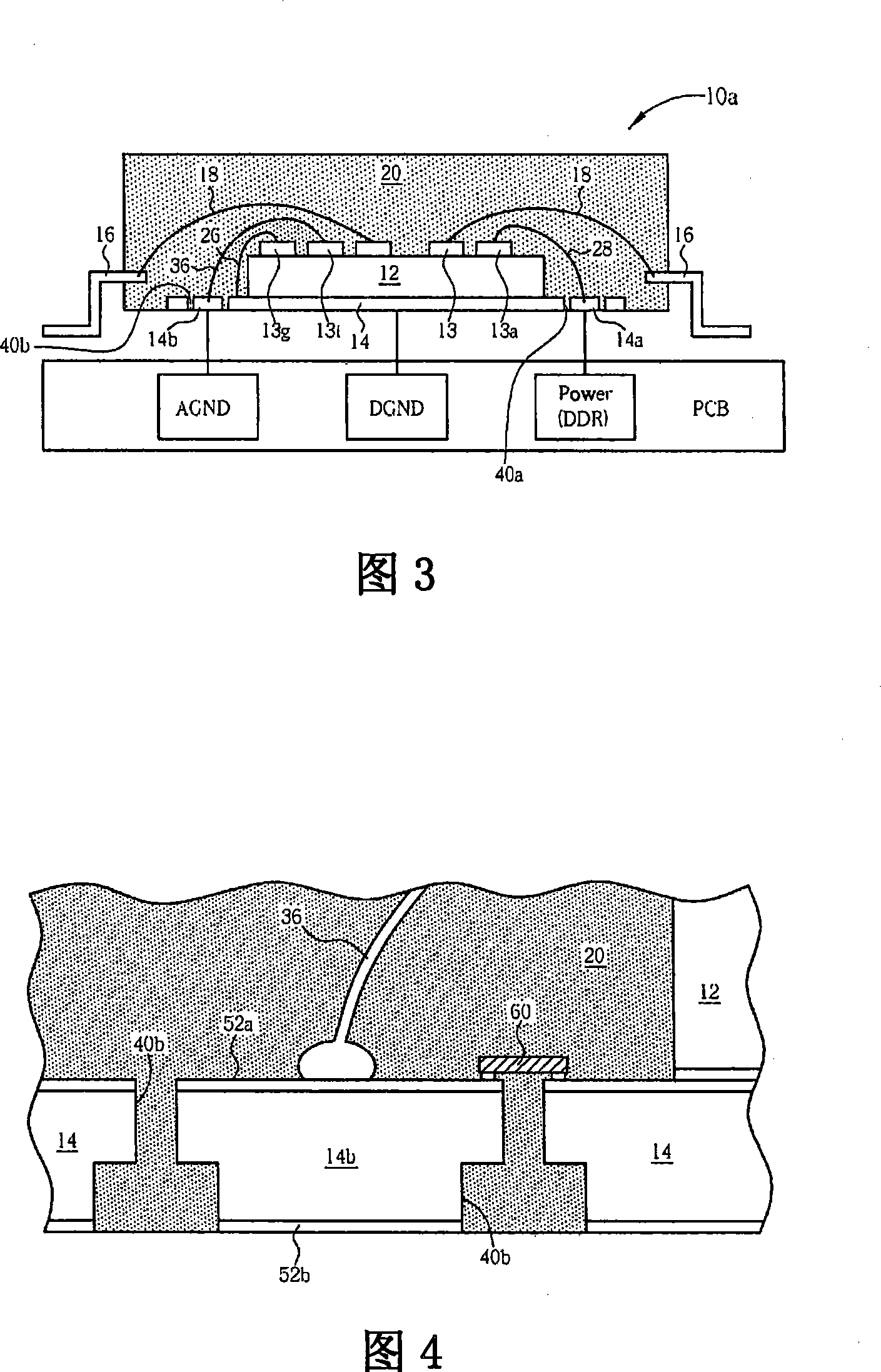

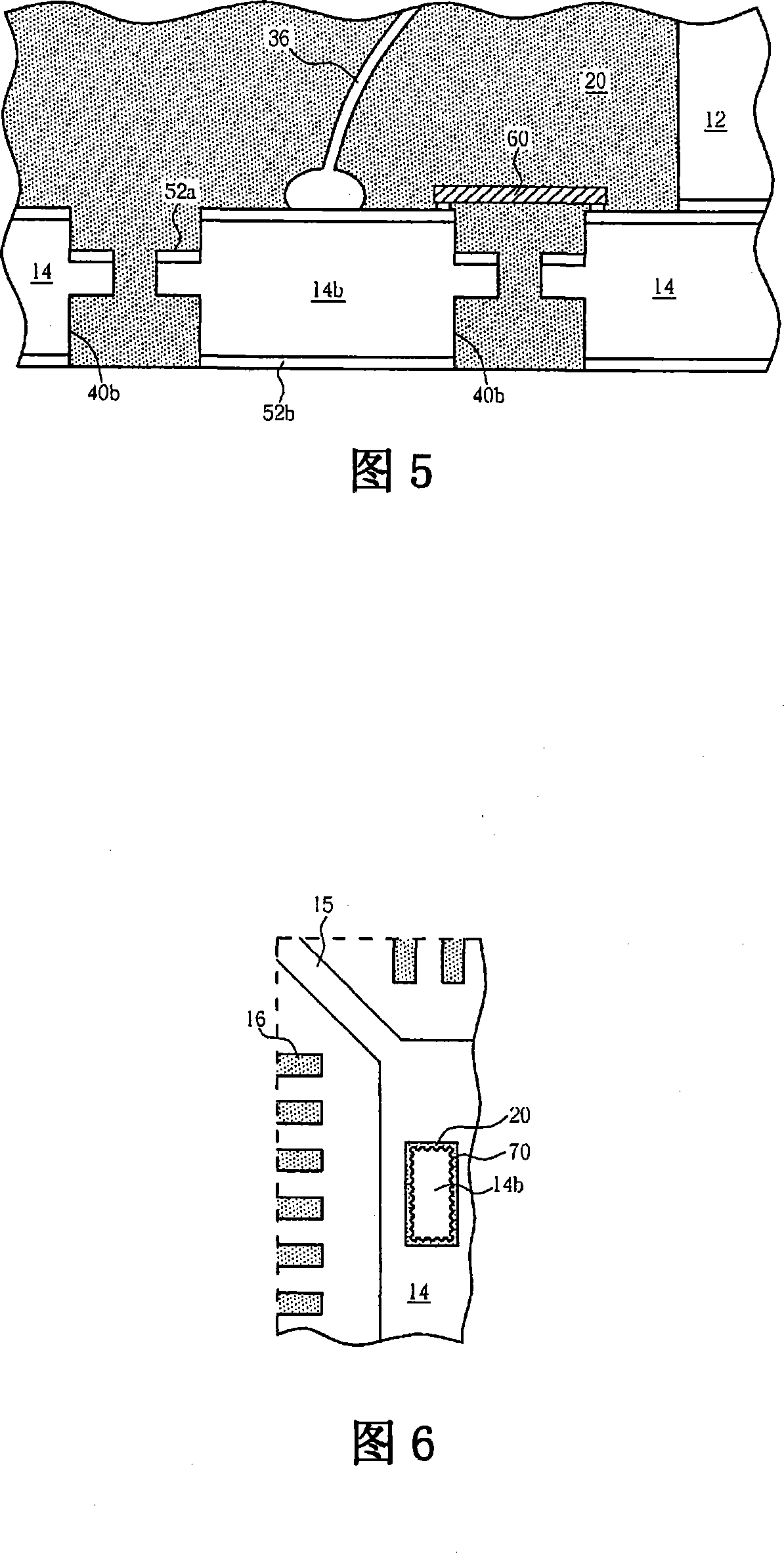

[0032] The leadframe (leadframe) package (packaging) structure described below can be used for, but not limited to, low-profile quad flat pack (LQFP) package, thin quad flat pack (Thin Quad Flat Pack, TQFP) package , Quad Flat Non-leaded (QFN) package, DFN package, multi-zone QFN (multi-zone QFN) package, multi-die package, and flip-chip packaging ).

[0033] Compared with the prior art, by saving or releasing the lead pads (ground pads), power pads (power pads) or other types of signal pads originally used to connect semiconductor chips, the present invention can Pushing the limits of leadframe structure packaging even further. In addition, the present invention can also be used to improve the electronic performance of integrated circuit packaged products by using a separate ground system on the die pad.

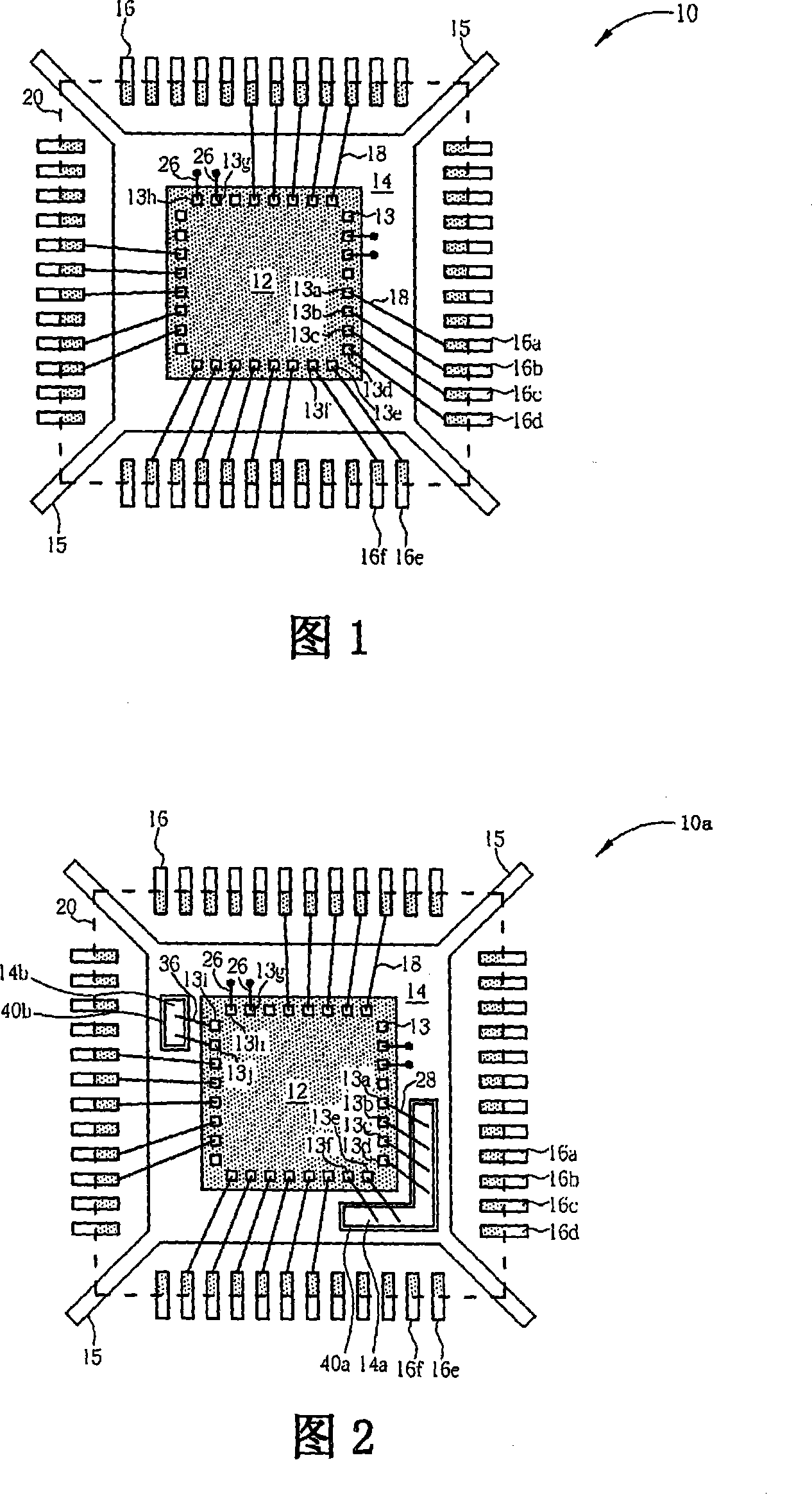

[0034] FIG. 1 illustrates a schematic top view of a leadframe package 10 . As shown in FIG. 1 , the lead frame package 10 includes a semiconductor die 12 as an example o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More