Semiconductor device and method for fabricating the same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., to achieve the effect of eliminating underlying dependencies and improving driving force

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0067] Next, the structure of the semiconductor device according to the first embodiment of the present invention will be described with reference to the drawings.

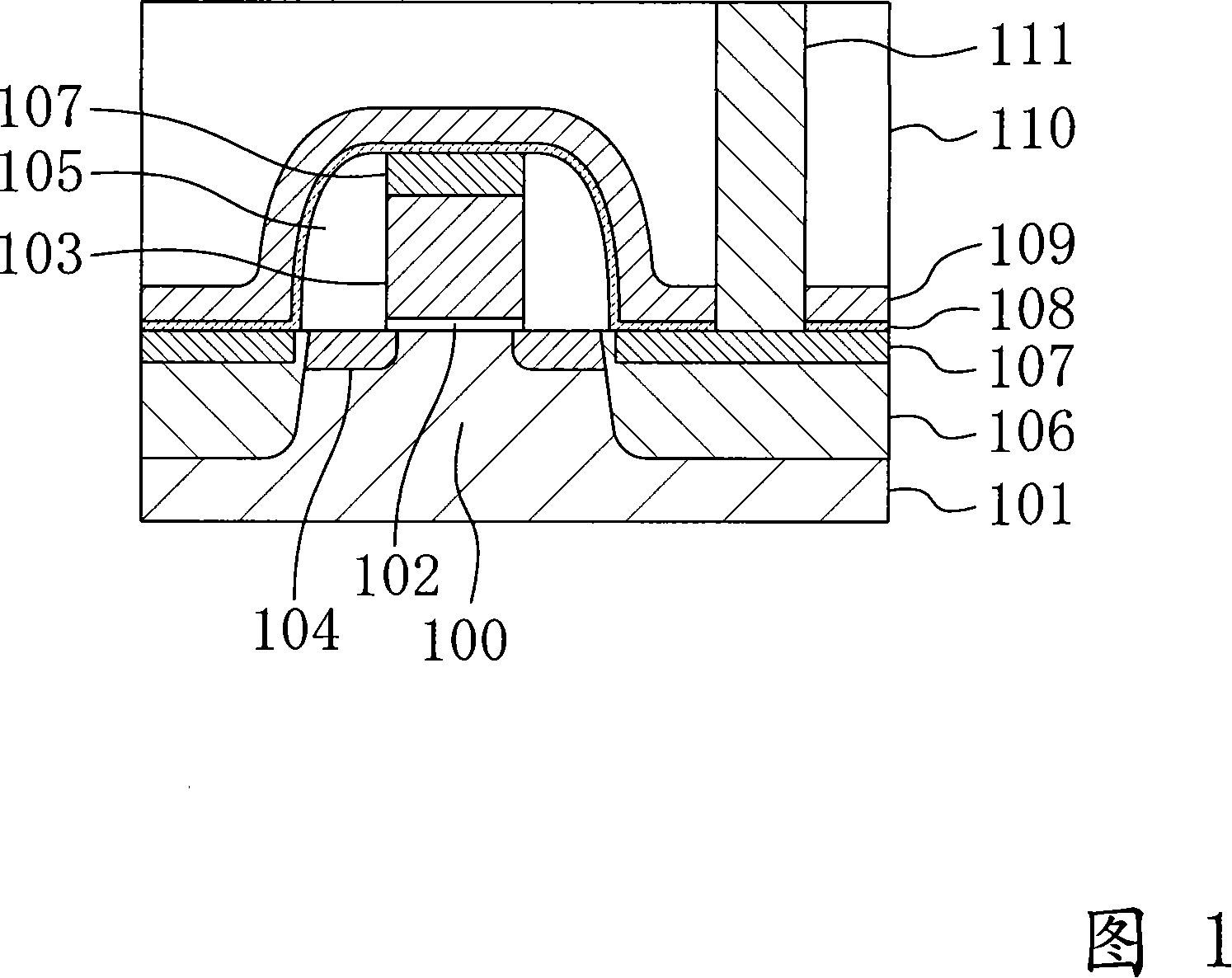

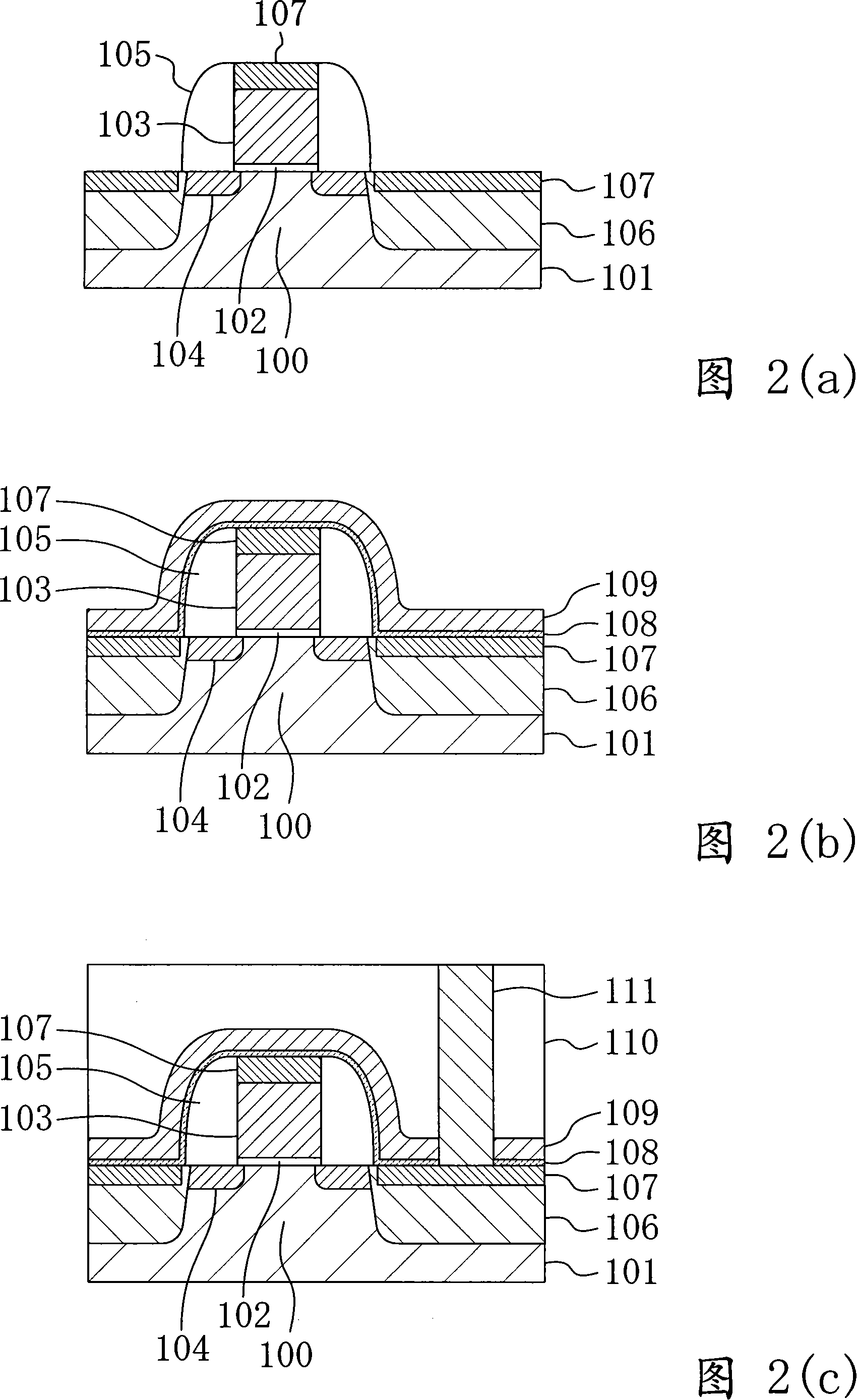

[0068] FIG. 1 is a schematic cross-sectional view showing the structure of a semiconductor device according to a first embodiment of the present invention.

[0069] As shown in FIG. 1 , in a semiconductor substrate 101 made of, for example, silicon, an active region 100 surrounded by an element isolation region (not shown) and having a p well (not shown) is formed, and on the active region 100 A gate electrode 103 having a silicide region 107 made of, for example, NiSi with a film thickness of about 20 nm is formed on an upper layer through a gate insulating film 102 made of, for example, a SiON-based film with a film thickness of about 2 nm. The film thickness of the electrode 103 is about 110 nm. Also, the gate length of the gate electrode 103 is about 50 nm. In the regions on both sides of the gate electrode ...

no. 2 example

[0091] Next, the structure of a semiconductor device according to a second embodiment of the present invention will be described with reference to the drawings.

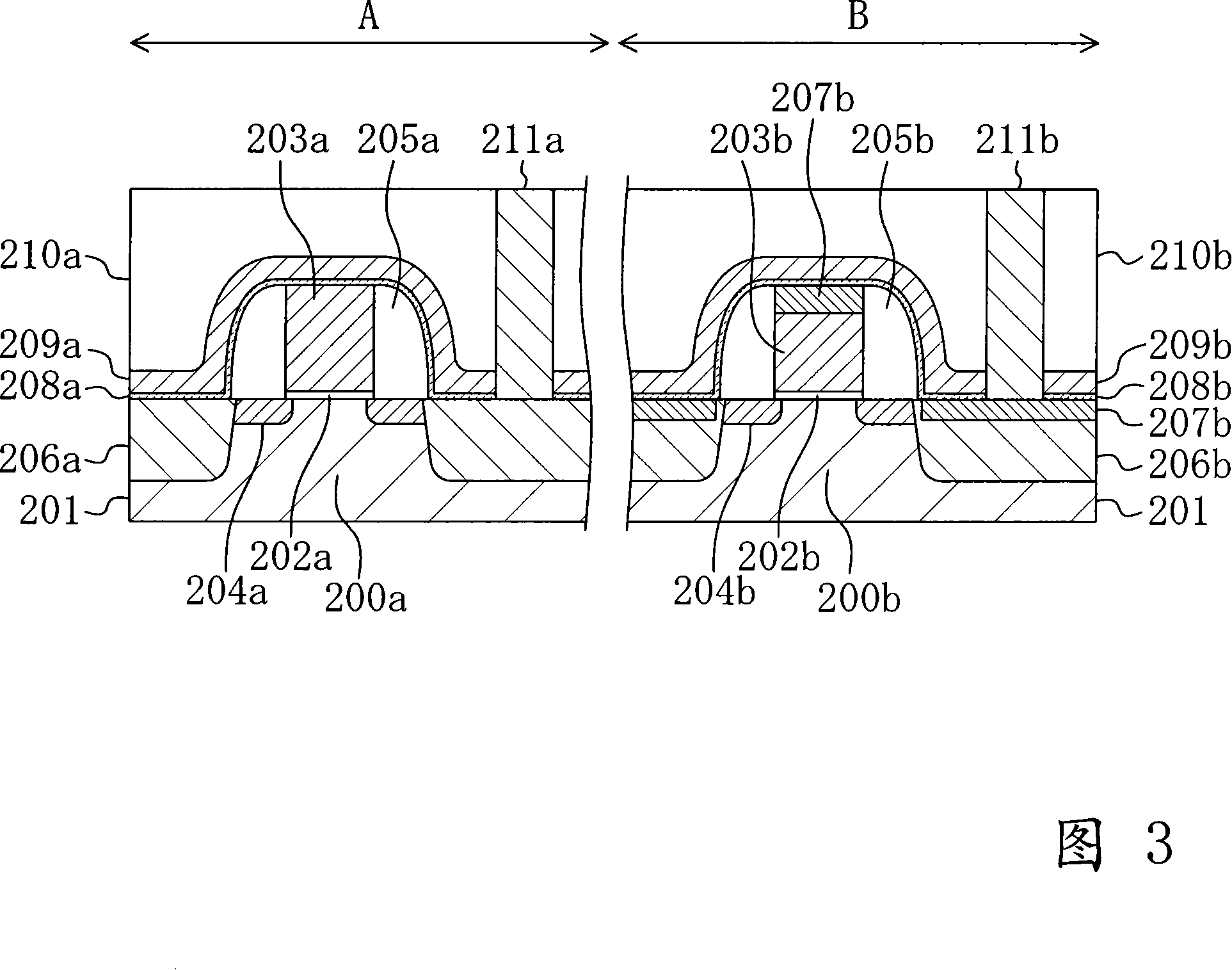

[0092] 3 is a schematic cross-sectional view showing the structure of a semiconductor device according to a second embodiment of the present invention.

[0093] In the region A in which the NMIS transistor is formed shown in FIG. 3 , in the semiconductor substrate 201 made of silicon, for example, an active region surrounded by an element isolation region (not shown) and in which a p-well (not shown) is formed is formed. 200a. On the active region 200a, a gate electrode 203a having a film thickness of approximately 120 nm is formed via a gate insulating film 202a made of, for example, a SiON-based film with a film thickness of approximately 2 nm. In addition, the gate length of the gate electrode 203a is about 50 nm.

[0094] In addition, in the regions on both sides of the gate electrode 203a in the active region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More