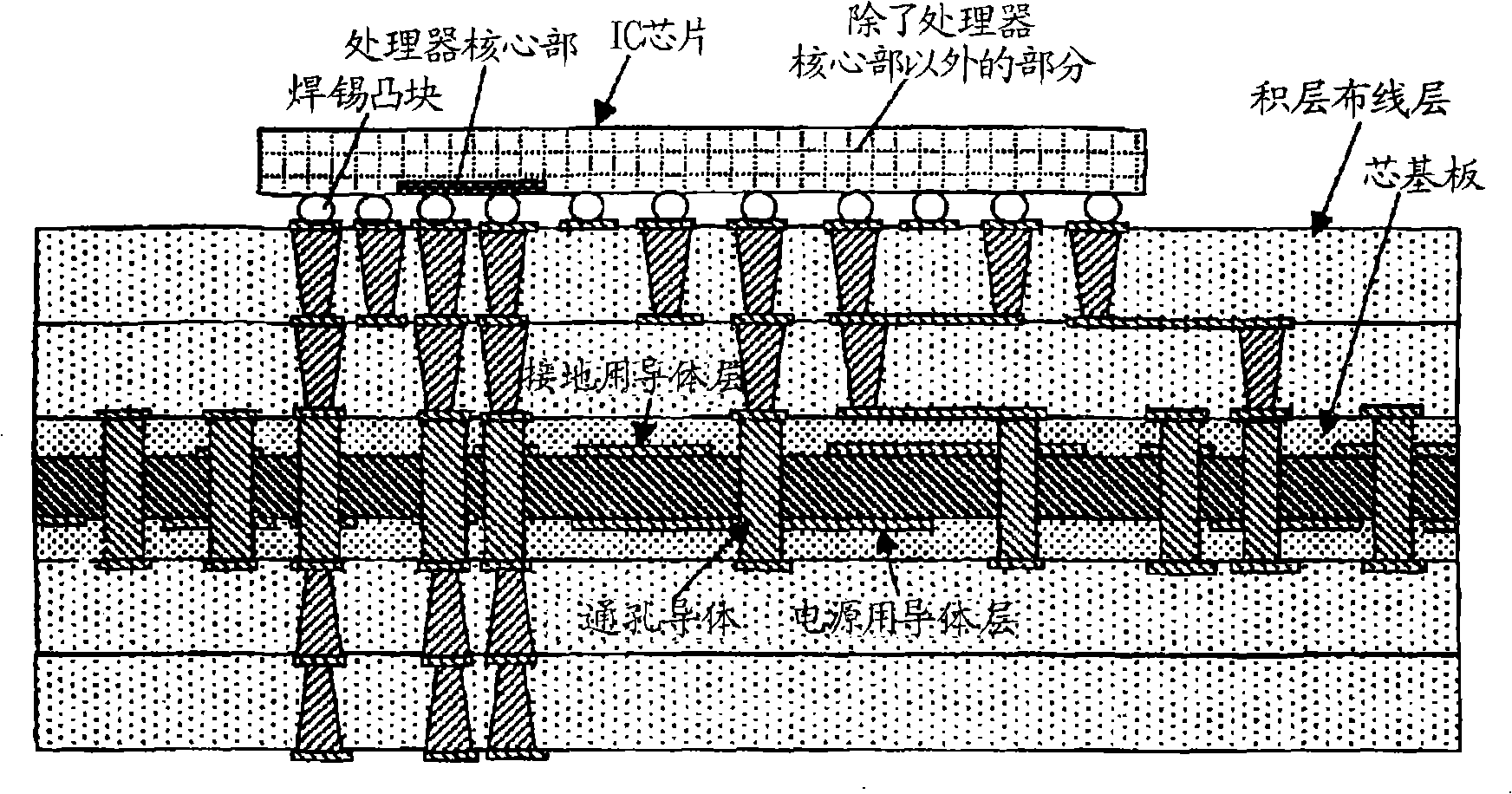

Multilayer printed wiring board

A multi-layer printing and circuit board technology, applied in the direction of printed circuit, printed circuit, printed circuit manufacturing, etc., can solve the problem of IC chip malfunction, and achieve the effect of causing malfunction, reducing mutual inductance, and suppressing the delay of power supply.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

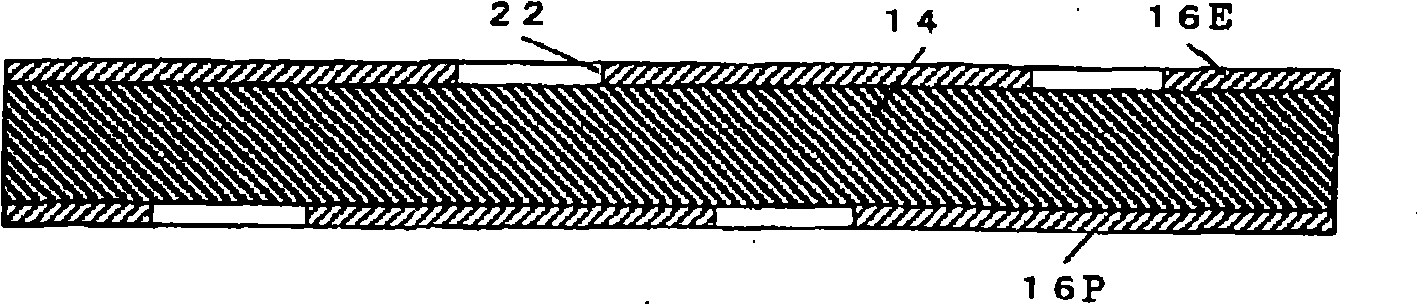

[0059] A. Preparation of resin composition for through-hole filling

[0060] By coating 100 parts by weight of bisphenol F-type epoxy monomer (manufactured by Yukashiel Co., molecular weight: 310, YL983U) on the surface, the average particle size of the silane coupling agent is 1.6 μm, and the maximum particle size is 15 μm or less. SiO 2 170 parts by weight of spherical particles (manufactured by Adotec, CRS 1101-CE) and 1.5 parts by weight of a leveling agent (manufactured by Sannopuko, Perenoru S4) were placed in a container, stirred and mixed to prepare It is a resin filling material whose viscosity is 44-49 Pa·s at 23±1°C. In addition, as a curing agent, 6.5 parts by weight of an imidazole curing agent (manufactured by Shikoku Chemicals Co., Ltd., 2E4MZ-CN) was used. As the resin for filling the through-holes, other thermosetting resins such as epoxy resins (for example, bisphenol F type and phenolic resin types), polyimide resins, and phenolic resins may be used. The ...

Embodiment 2

[0128] In the step (5) of Example 1, the pitch for forming via-hole conductors was changed. Via-hole conductors are not formed directly under all pads directly under the processor core portion 80a (via-hole conductors can be formed within a range of 50 to 100% of the number of pads directly under the processor core portion), but The via-hole conductors are formed every other land, and therefore, the pitch is 250 μm. Via-hole conductors are formed at a pitch of 300 to 600 μm to account for 10% of the number of pads except directly below the processor core 80 a in the region other than directly below the processor core 80 a. Except for this, a multilayer printed wiring board was produced in the same manner as in Example 1.

Embodiment 3

[0130] In step (5) of Example 1, the number of through-holes for forming via-hole conductors was changed. Directly below the processor core unit 80a is the same as that of the first embodiment. In the region other than directly under the processor core part, 50% of via conductors are formed with respect to the number of pads except directly under the processor core part 80a. Immediately below the IC chip 80, directly under the portion 80b other than the processor core portion 80a, via-hole conductors are formed at a pitch of 150 to 400 μm, and at the portion other than the IC chip 80, formed at a pitch of 300 to 600 μm. The spacing forms via conductors. Except for this, a multilayer printed wiring board was produced in the same manner as in Example 1.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Current density | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More