Data communication circuit with equalization control

一种数据信号、电路的技术,应用在信号的频率相关失真领域,能够解决消耗模拟电路面积、消耗功率和硅面积、均衡器调谐未对准等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

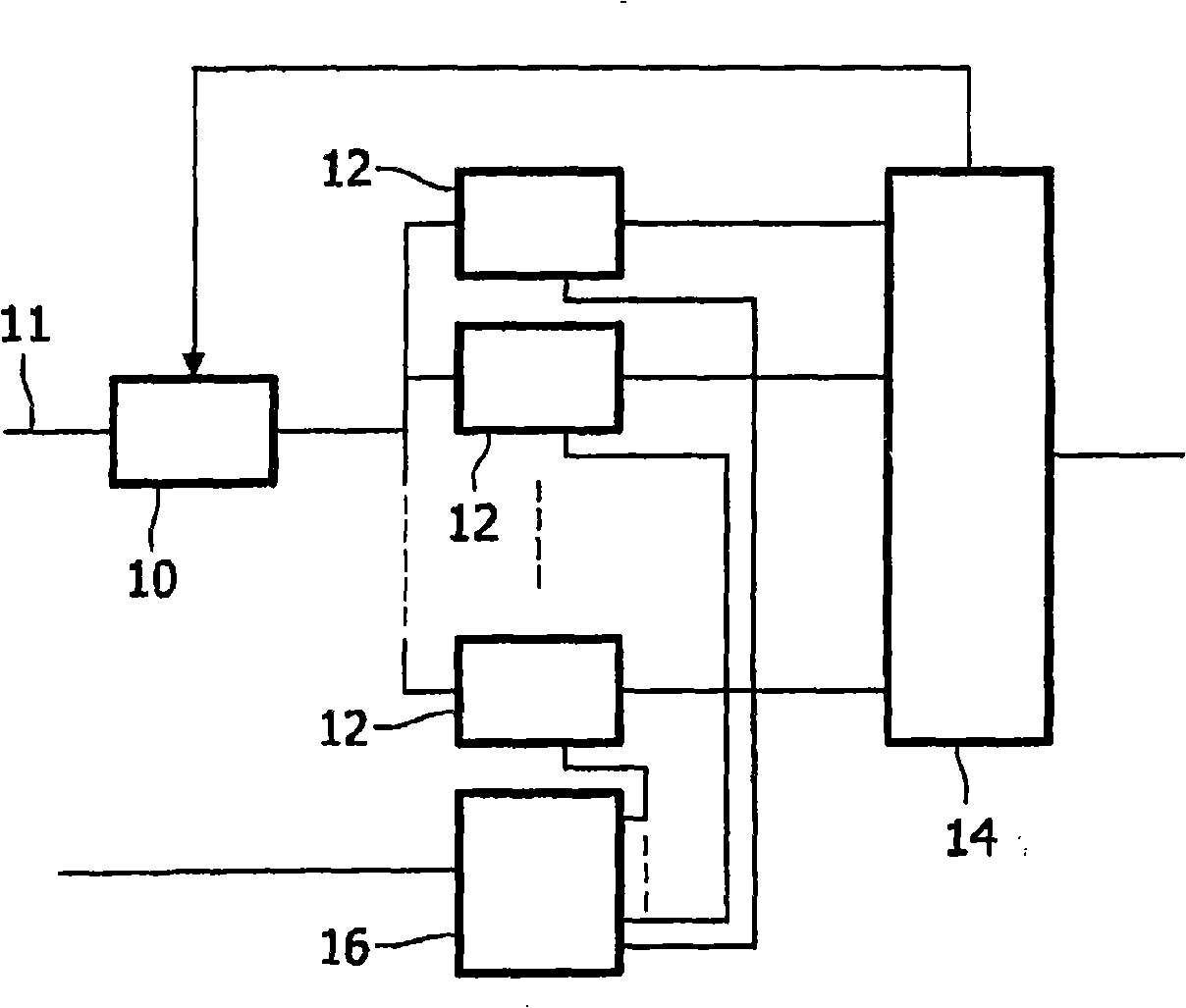

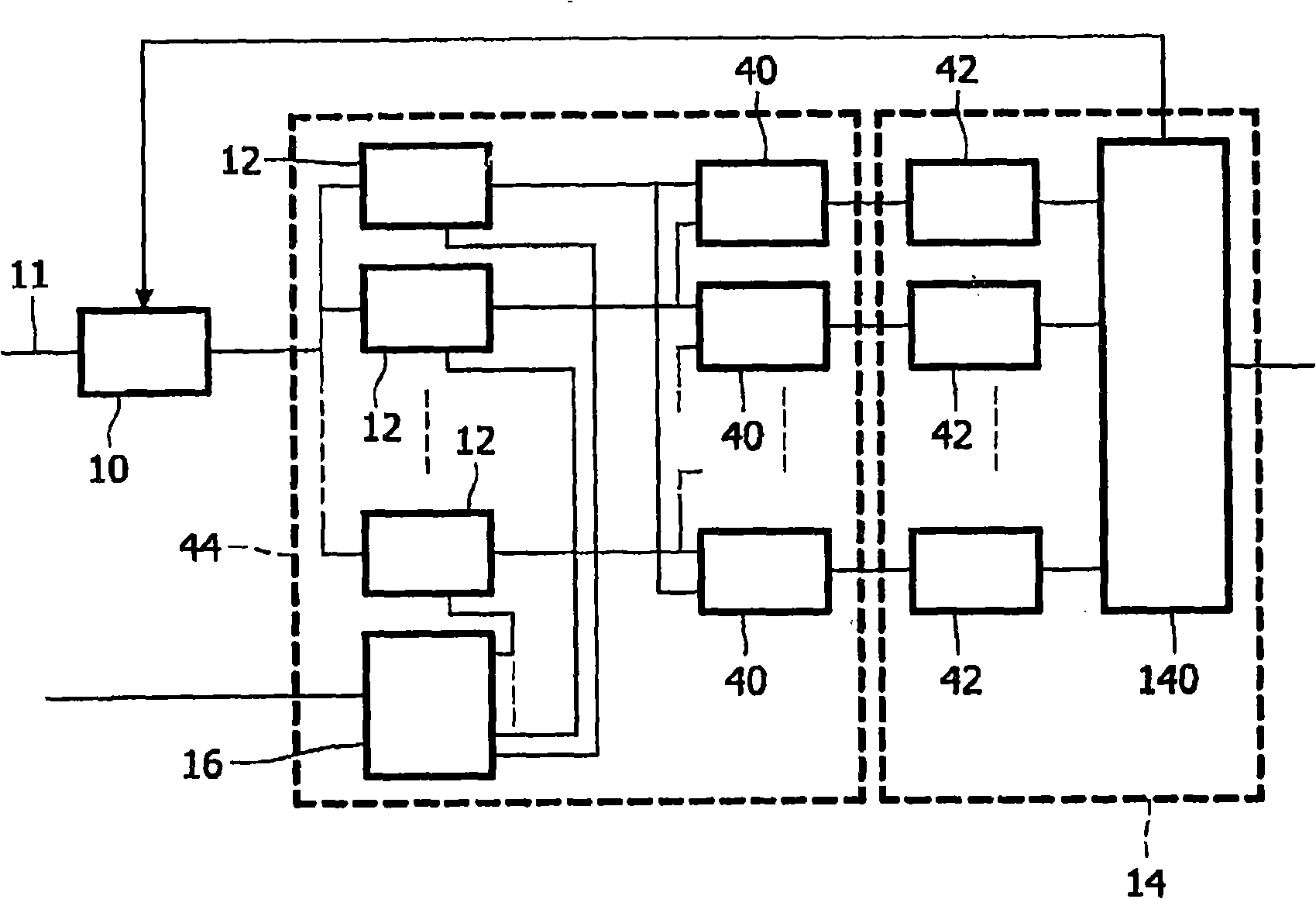

[0033] figure 1 A simplified block diagram of the receiver circuit for synchronous reception is shown. The circuit includes an adaptable equalizer 10 , a plurality of sampling amplifiers or samplers 12 , a digital post-processing circuit 14 , and a clock recovery circuit 16 . A circuit input 11 is coupled to a signal input of an equalizer 10 having an output coupled to each sampling amplifier 12 . The output of the sampling amplifier 12 is coupled to a digital post-processing circuit 14 . The digital post-processing circuit 14 has a first output coupled to the signal output 15 of the circuit and a second output coupled to the setting input of the equalizer 10 . Clock recovery circuit 16 has an output coupled to sampling amplifier 12 . The input of the clock recovery circuit may be coupled to the circuit input 11, or to an external clock source, or to a switch for selecting between the circuit input 11 and the external clock source. As an alternative to the clock recovery c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More