Wafer level package of electronic element and manufacturing method thereof

A wafer-level packaging and electronic component technology, applied in electrical components, semiconductor/solid-state device manufacturing, electrical solid-state devices, etc., can solve problems such as peeling, and achieve the effect of improving adhesion and conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

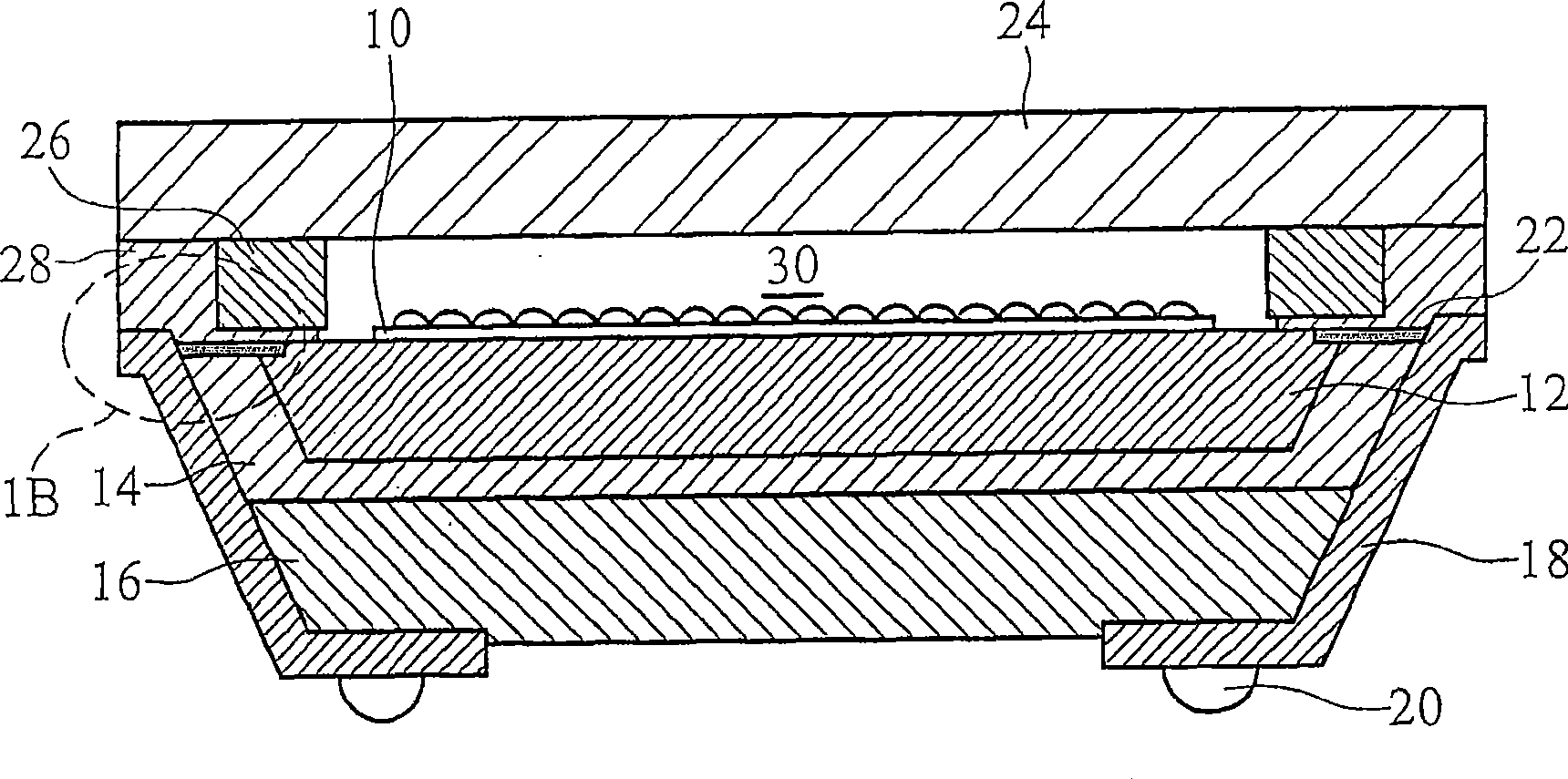

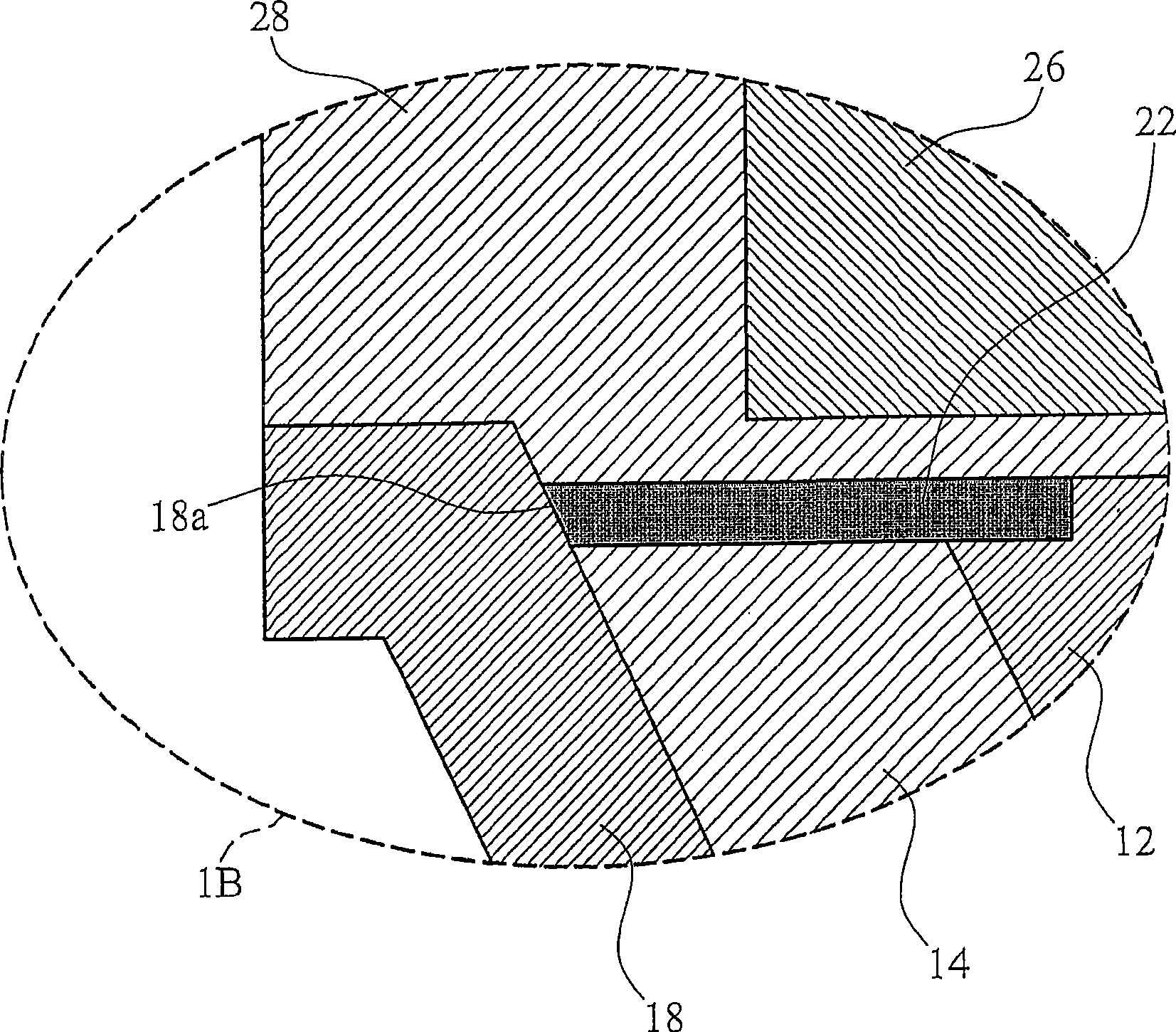

[0043] The following examples are described in detail with various embodiments and accompanying drawings, which serve as a reference basis for the present invention. In the drawings or descriptions in the specification, the same reference numerals are used for similar or identical parts. And in the drawings, the shapes or thicknesses of the embodiments may be enlarged for simplification or convenient labeling. In addition, the parts of each element in the drawings will be described separately. It should be noted that the elements not shown or described in the drawings are forms known to those skilled in the art. In addition, the specific embodiment is only The disclosure of a specific method used in the present invention is not intended to limit the present invention.

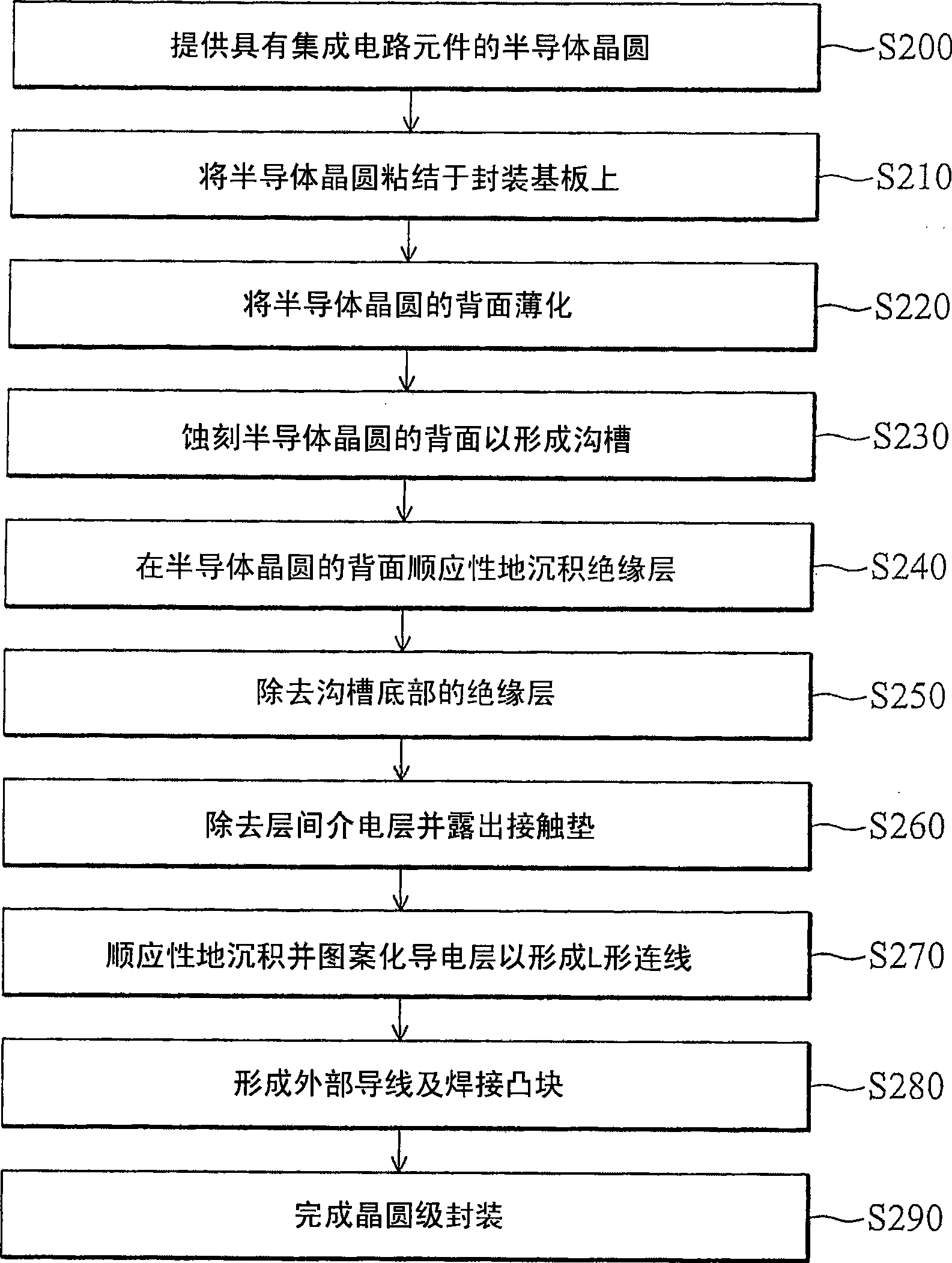

[0044] figure 2A flowchart showing a method for manufacturing wafer-level packaging of electronic components according to an embodiment of the present invention. First in step S200, a semiconductor wafer wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com