High-efficiency simulating and verifying device for large test and excitation

A technology of test stimulation and simulation verification, which is applied in special data processing applications, instruments, electrical digital data processing, etc., and can solve the problems of unsatisfactory verification speed, limited operating speed, high-performance microprocessors that can only reach several beats per second, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0004] First, develop a file format for the reserved file that holds the visible state of the processor software (such as figure 2 ), determine the storage location, size and encoding method of the processor's internal structure registers, control and status registers, TLB entries, memory contents, external I / O register contents, and specific environmental parameters in the file.

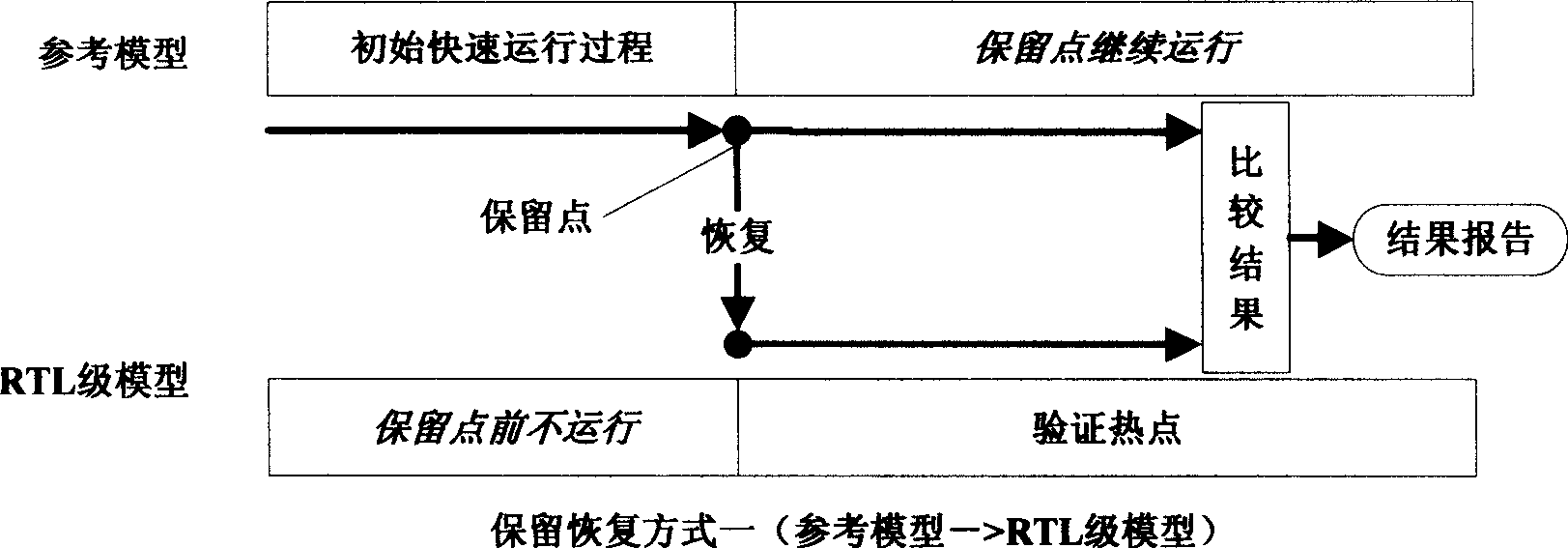

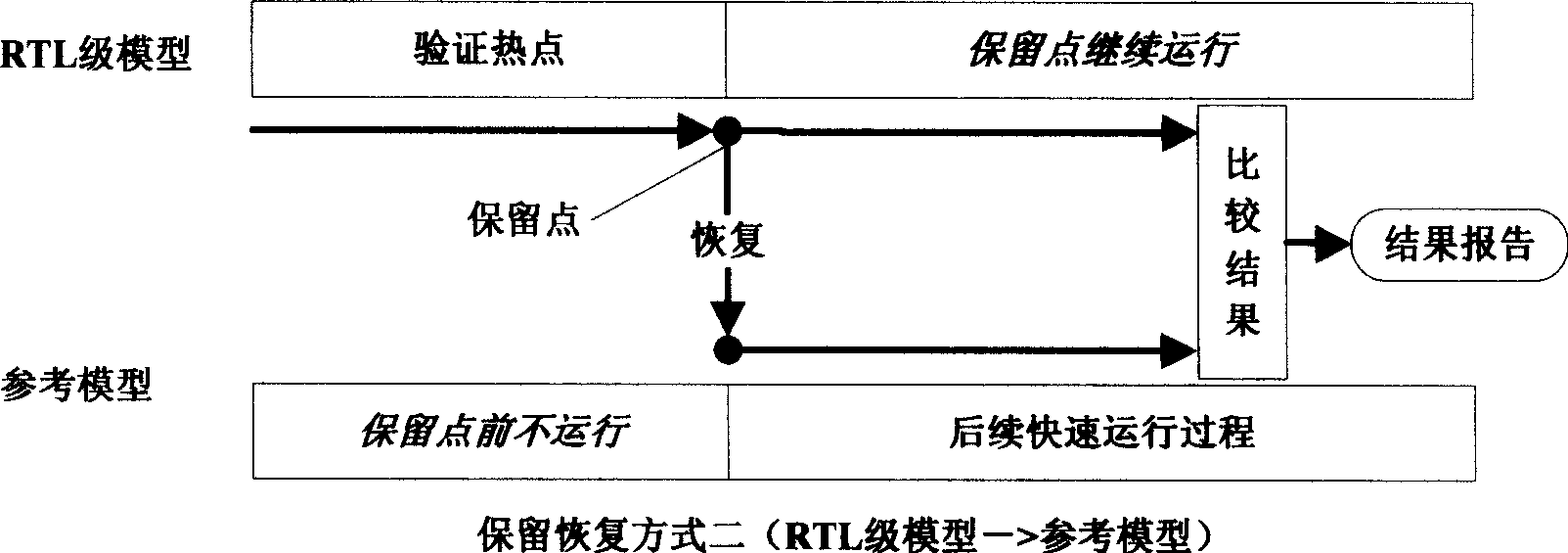

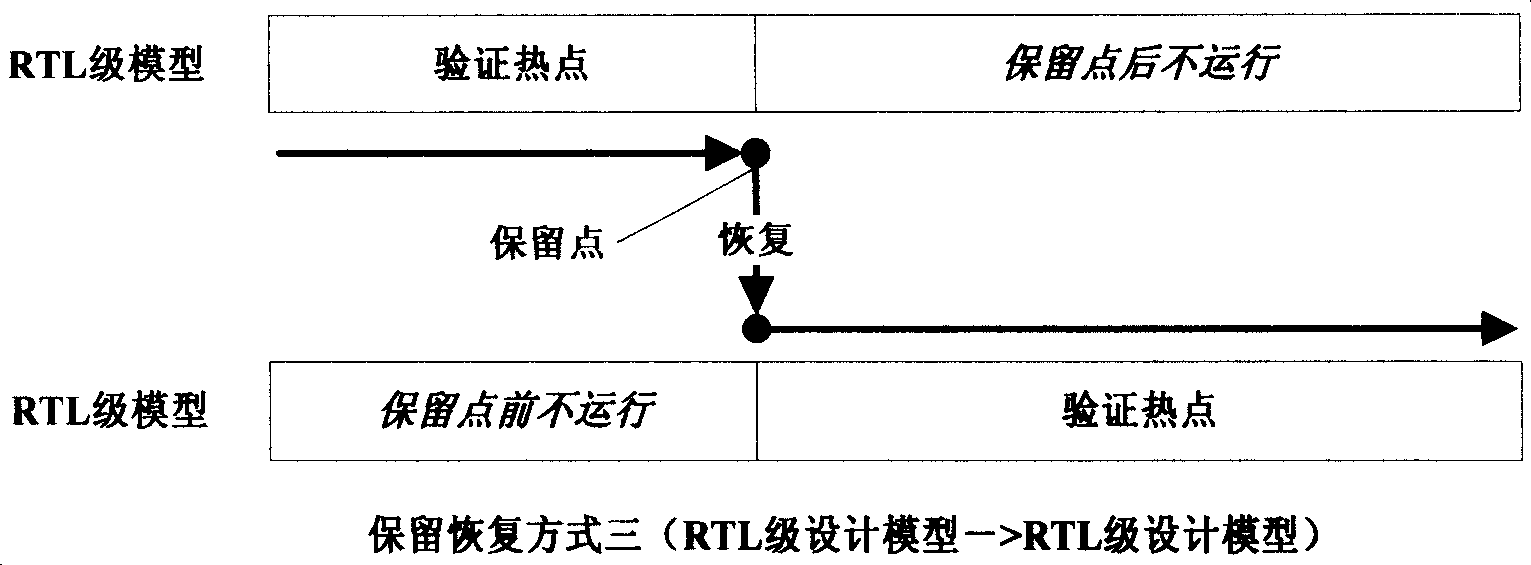

[0005] Secondly, based on the state preservation file format, the state preservation function save_state() and the state restoration function restore_state() are implemented in the reference model respectively, and the state preservation task save_state() and state preservation task save_state() and state are respectively implemented in the testbench of the RTL simulation environment The restore task restore_state() ensures that the state preservation files generated by the save_state() modules of the two models can be correctly read and restored by the restore_state() modules of the two models, achi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More