Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as inability to apply strain technology and inability to realize channel regions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

[0041] (1) About the manufacturing process

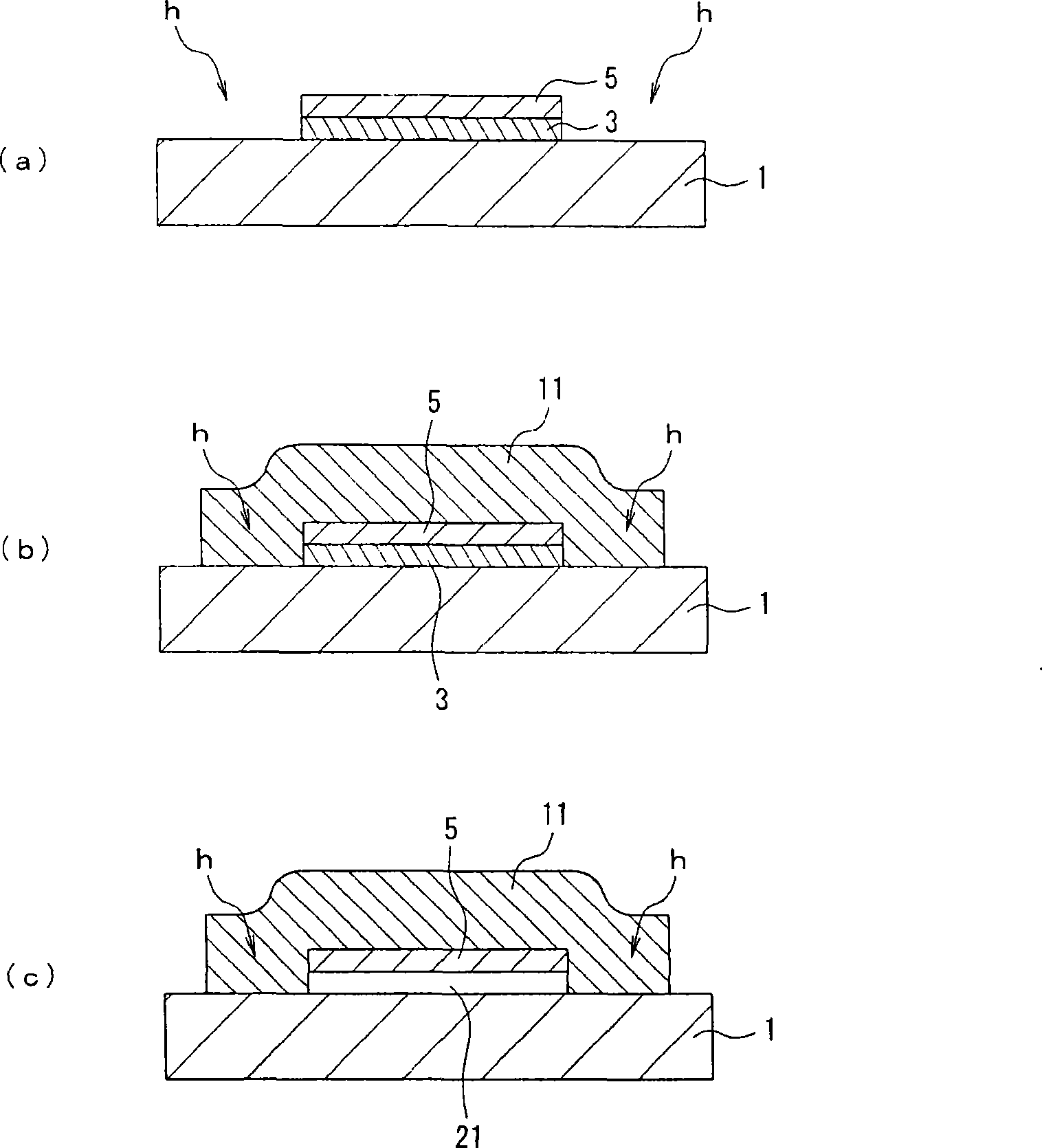

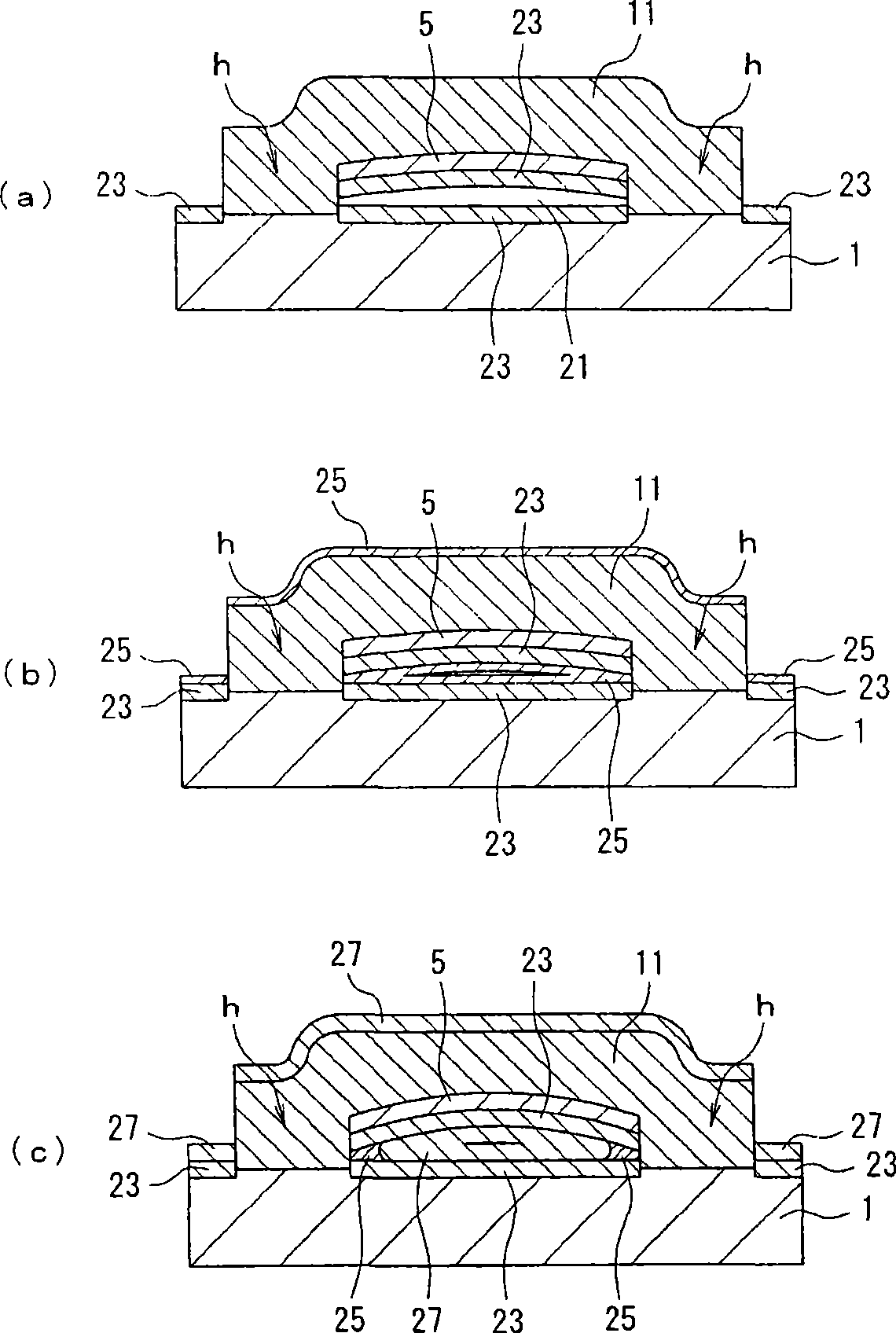

[0042] figure 1 (a)~ figure 2 (c) is a cross-sectional view illustrating a method of manufacturing a semiconductor device according to an embodiment of the present invention.

[0043] First, in figure 1 In (a), a germanium silicide (SiGe) layer 3 is formed on a bulk silicon (Si) substrate 1, and a single crystal silicon (Si) layer 5 is formed thereon. These SiGe layer 3 and Si layer 5 are continuously formed by, for example, an epitaxial growth method. Next, the Si layer 5 and the SiGe layer 3 are partially etched respectively by photolithography technology and etching technology. As a result, the support hole h having the Si substrate 1 as the bottom surface is formed in a region overlapping with the element isolation region (that is, the region where the SOI structure is not formed) in plan view. In this etching st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More