Electrical level translation circuit

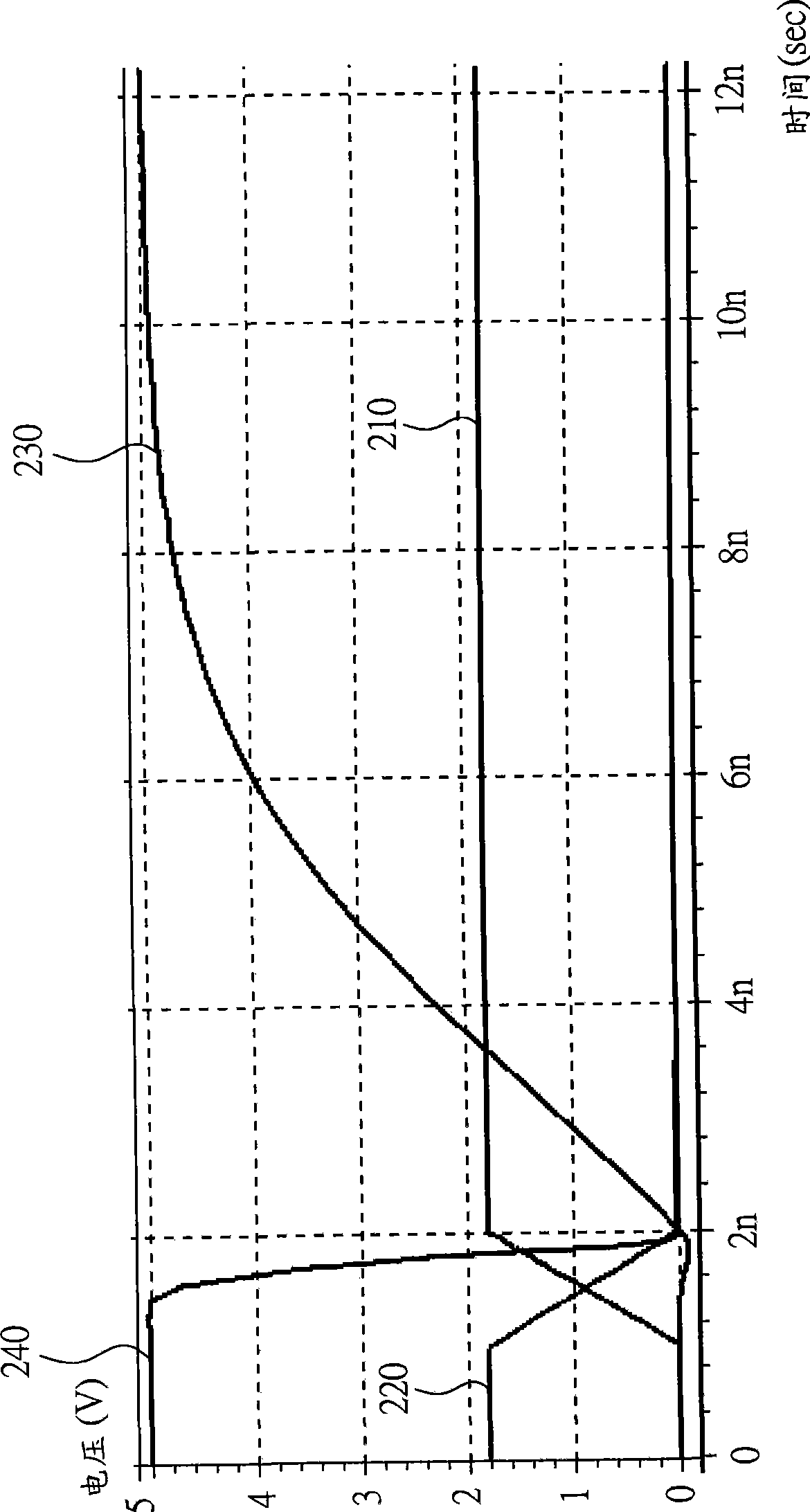

A technology for converting circuits and levels, applied in the direction of logic circuits, logic circuit connection/interface layout, electrical components, etc., can solve the problems of power consumption, slow level conversion circuit 10, pulling, etc., to achieve the effect of improving the conversion speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

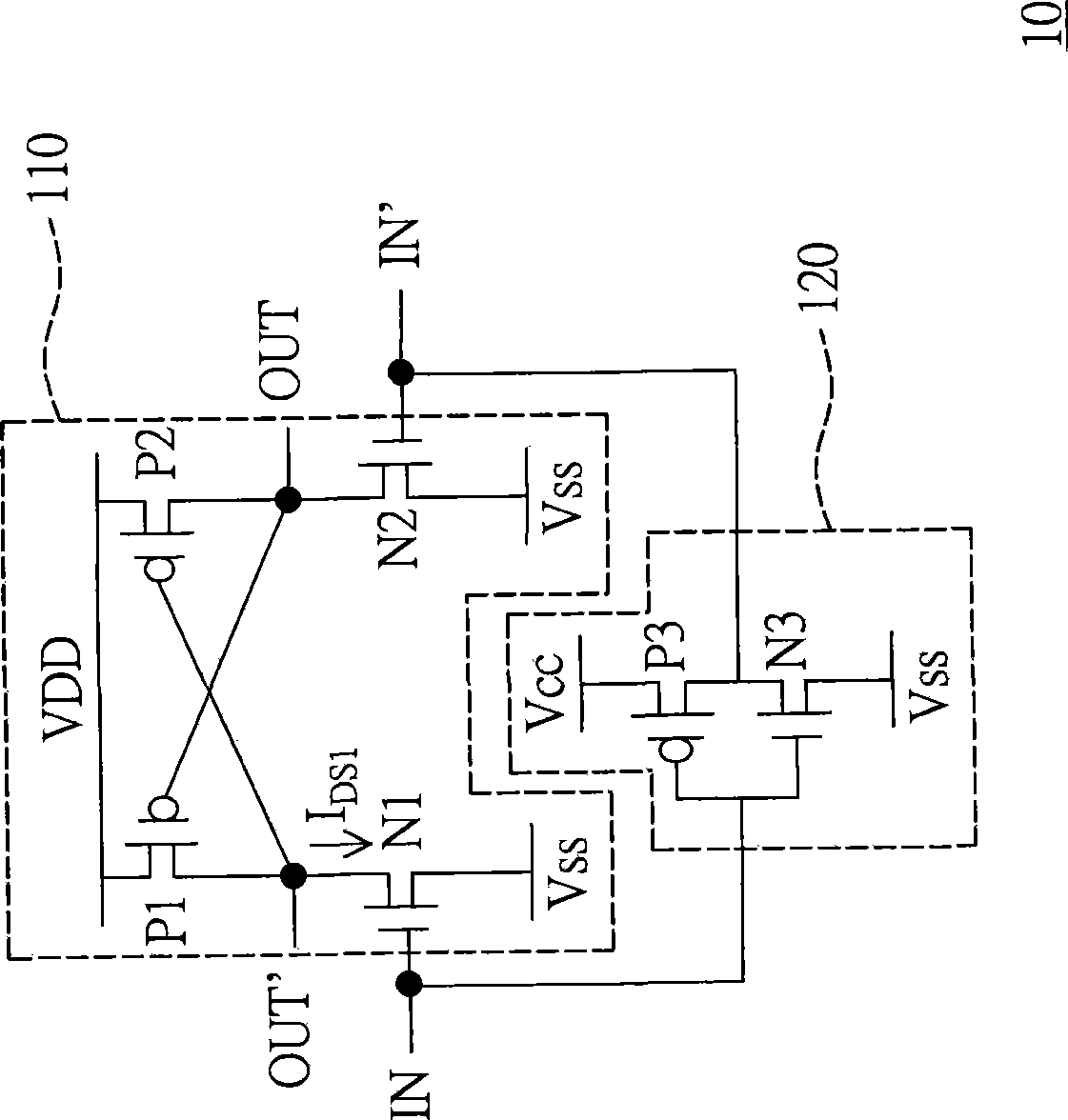

[0056] Please refer to Figure 5 , which shows a circuit diagram of a level conversion circuit according to Embodiment 1 of the present invention. The aforementioned level shifting circuit 40 and inverter 420 are represented by level shifting circuit 50 and inverter 520 respectively in Embodiment 1, and the first switch circuit 430 and the second switch circuit 440 are respectively represented by A first switch circuit 530 and a second switch circuit 540 are shown. For the convenience of description, the following description takes the input signal IN and the inverted input signal IN' between 0-1.8V as an example. In addition, it is illustrated by taking the output signal OUT and the inverted output signal OUT' between 0V and 5V as an example.

[0057] The first switch circuit 530 further includes a transistor N3, and the transistor N3 is, for example, an N-type metal oxide semiconductor transistor. The first terminal of the transistor N3 is coupled to the control terminal ...

Embodiment 2

[0067] Please refer to Figure 8 , which shows a circuit diagram of a level conversion circuit according to Embodiment 2 of the present invention. The aforementioned level conversion circuit 40 and inverter 420 are represented by level conversion circuit 90 and inverter 920 respectively in the second embodiment, and the first switch circuit 430 and the second switch circuit 440 are respectively represented in the second embodiment It is represented by a first switch circuit 930 and a second switch circuit 940 .

[0068] The first switch circuit 930 further includes a transistor N3 and a transistor N4, and the transistor N3 and the transistor N4 are, for example, N-type metal oxide semiconductor transistors. The transistor N3 is connected in series with the transistor N4, and the first terminal of the transistor N3 is coupled to the control terminal of the transistor P2. The second terminal of the transistor N3 is coupled to the first terminal of the transistor N4, and the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com