Multi-chip stacking method for halving routing procedure and structure thereof

A multi-chip and chip technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as easy punching of bonding wires and inability to omit wire bonding processes, etc., to achieve narrow gaps, The effect of reducing chip stack height and enhancing bonding force

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

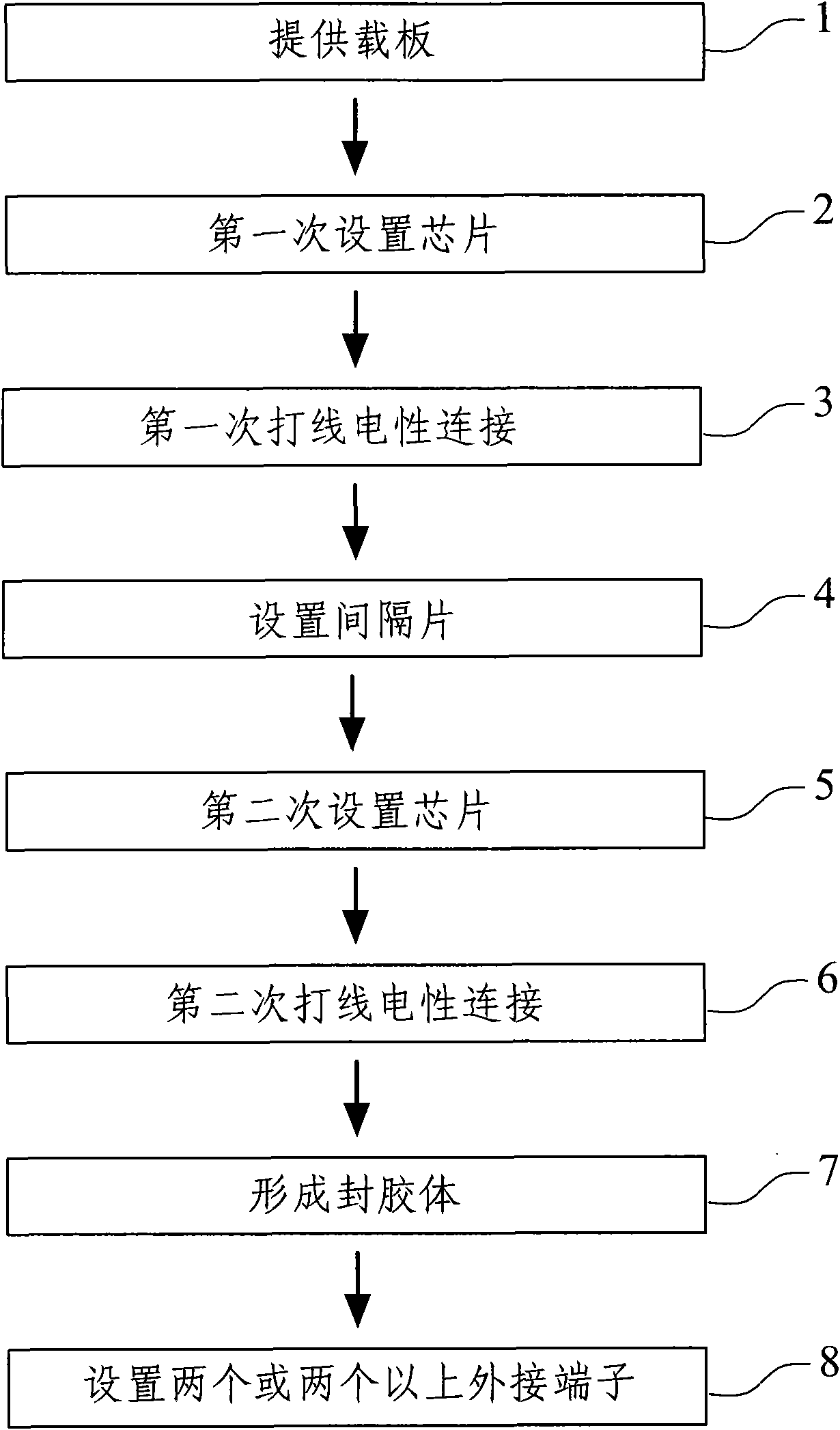

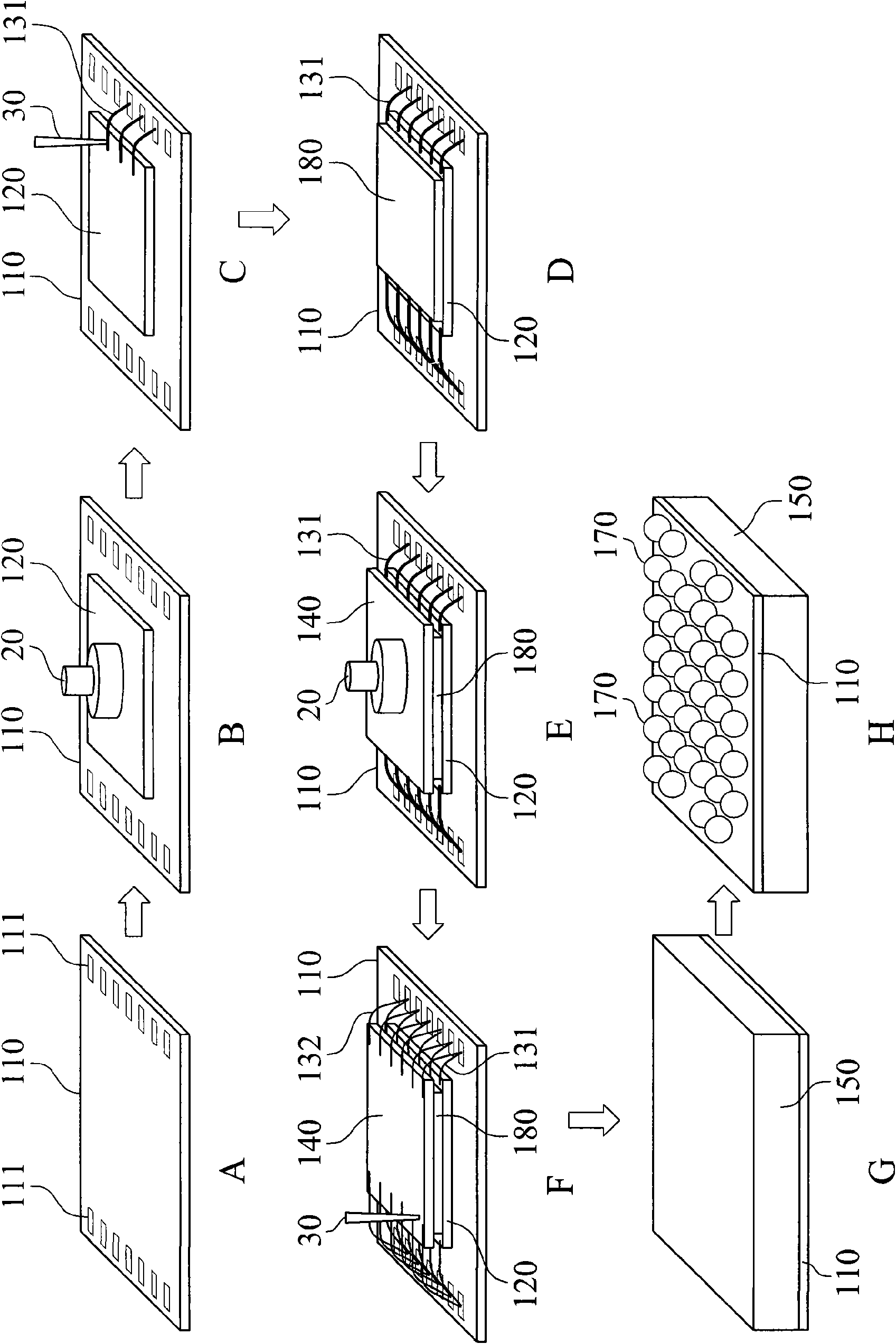

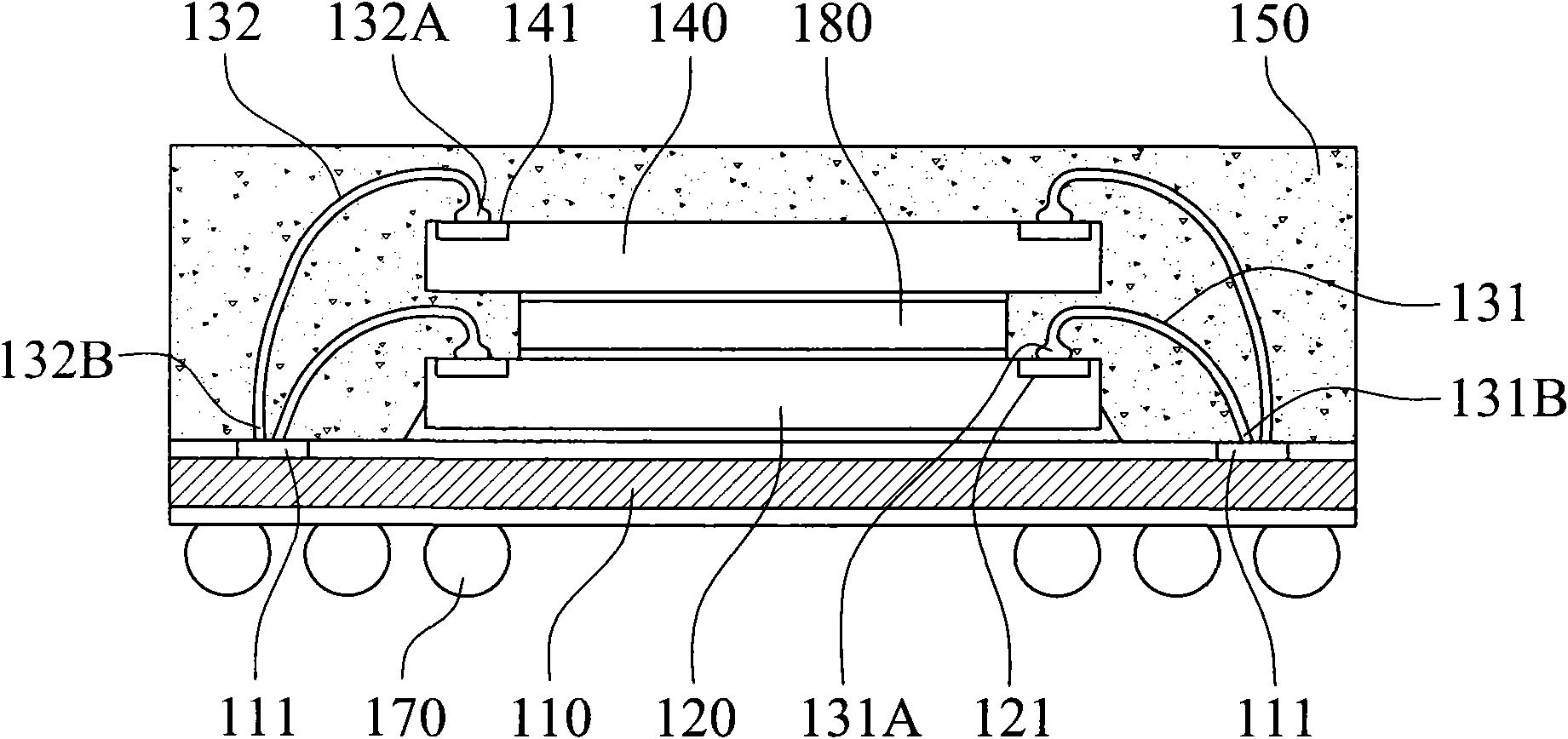

[0090] According to the first specific embodiment of the present invention, with reference to Figure 4 and Figure 5 , specifically disclosing a multi-chip stacking method in which the wire bonding process is halved.

[0091] see Figure 4 As shown, a multi-chip stacking method mainly includes the following steps: Step 11, providing a carrier board; Step 12, setting up chips for the first time; Step 13, making electrical connections with wires; Step 14, forming a filling glue; Step 15, the first Secondary setting of chips and electrical connection; Step 16, forming a sealing body; Step 17, setting two or more external terminals. Among them, the step 14 of "forming the filling glue" is an unnecessary step, so in different embodiments, the step 14 of "forming the filling glue", the step 16 of "forming the sealing body" and the step of "setting two or more circumscribed Terminal" step 17 can be omitted or replaced. The component composition relationship in each step can be f...

no. 2 Embodiment

[0106] According to the second embodiment of the present invention, another multi-chip stacking method and structure that reduces the wiring process by half is disclosed.

[0107] First, see Figure 10 As shown in Figure A, a carrier board 310 is provided, and the carrier board 310 has two or more fingers 311 . In this embodiment, the fingers 311 can be formed in the central area of the carrier 310 .

[0108] Afterwards, see Figure 10 Figure B in and Figure 11 As shown, at least one first chip 320 is set on the carrier 310 by using the chip suction nozzle 40. In this embodiment, the first chip 320 can be two or more, and the fingers 311 are located on these first chips. Between the chips 320 , these fingers 311 can be shared by wire bonding, so the number of these fingers 311 can be reduced to reduce the cost of the carrier 310 . Such as Figure 11 As shown, each first chip 320 has two or more than two first electrodes 321 . The first electrodes 321 can be arranged i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More