Defect test structure of semiconductor device, defect test method and defect test structure of before-metal medium layer

A defect testing, semiconductor technology, applied in the direction of semiconductor/solid-state device testing/measurement, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of device short circuit, reduced efficiency, expensive, etc., to reduce costs and save test steps , the effect of improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

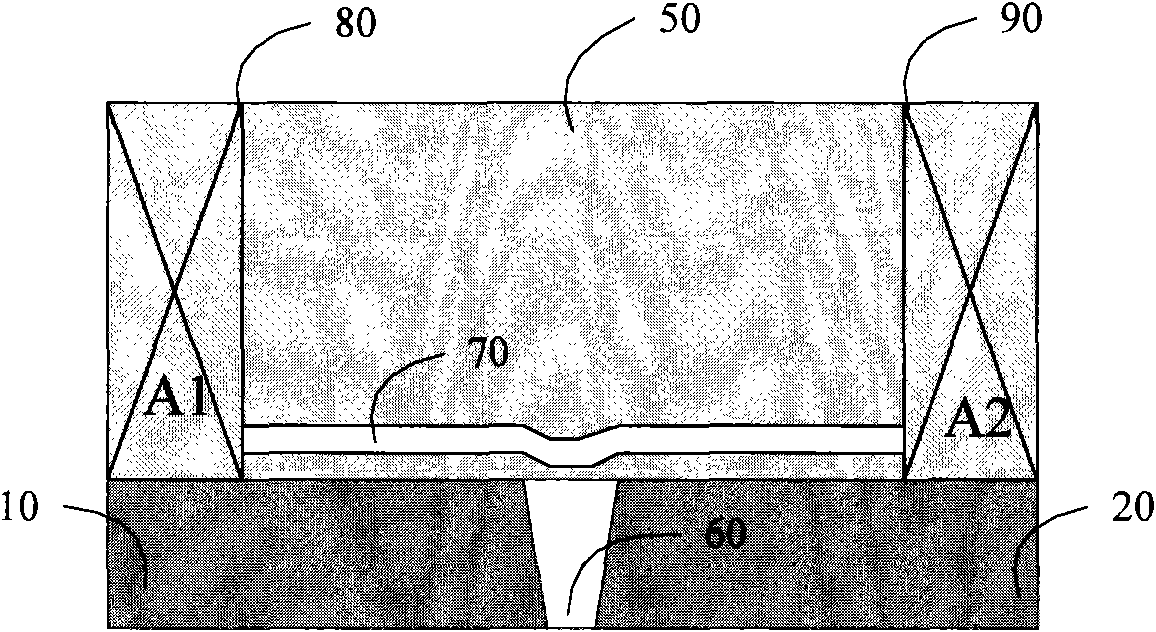

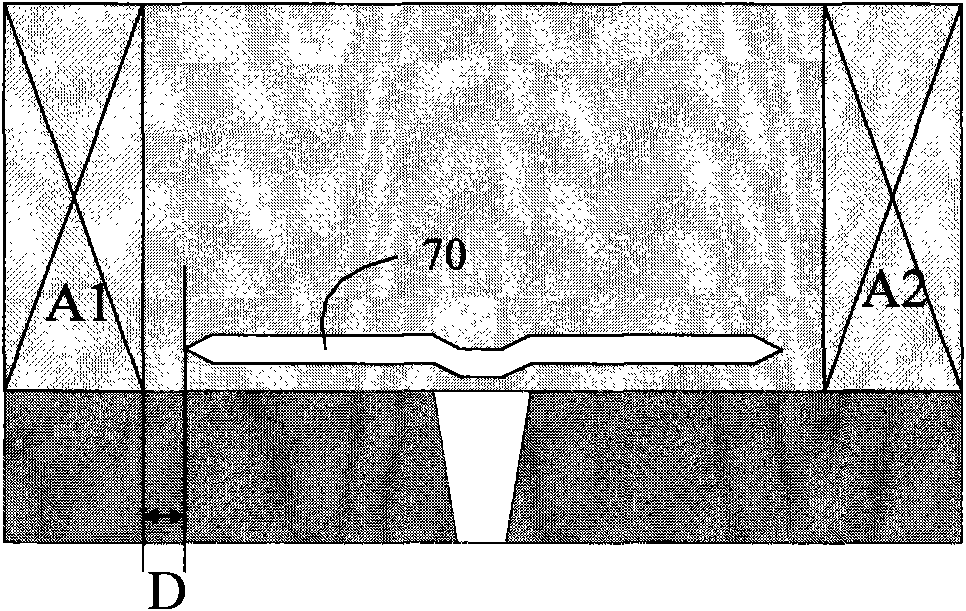

[0071] In this embodiment, the detection of void defects in the pre-metal dielectric layer is taken as an example, combined with the attached Figure 4 to Figure 7 A defect test structure and a defect test method of a semiconductor device are described in detail.

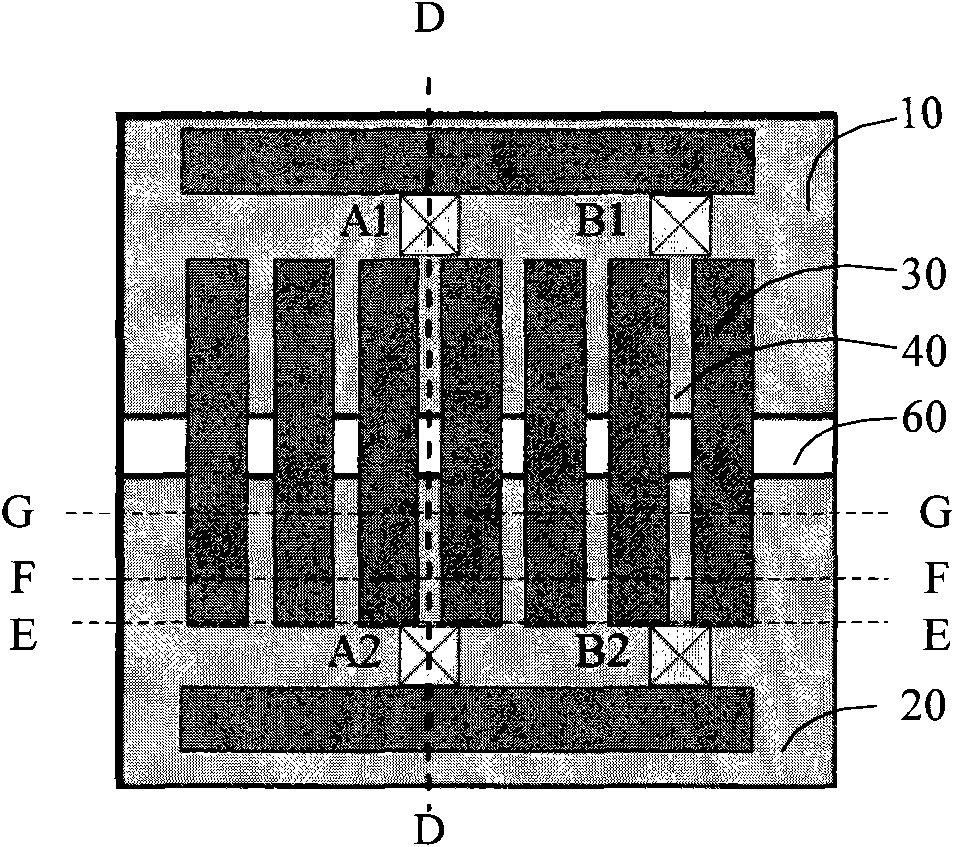

[0072] In this embodiment, the defect testing structure of the semiconductor device is used to test void defects in the pre-metal dielectric layer, and the defect testing structure of the semiconductor device is the defect testing structure of the pre-metal dielectric layer. Figure 4 It is a top view of the defect test structure of the pre-metal dielectric layer, the defect test structure includes: a semiconductor substrate (not shown in the figure), an active region 110 and an active region 120 on the substrate, and the active region 110 and the shallow trench isolation region 130 between the active region 120, the active region 110 and 24 parallel gates 140 above the active region 120, and the 23 parallel gates 1...

Embodiment 2

[0088] This embodiment takes testing the void defect in the shallow trench isolation region as an example, combined with the attached Figure 8 to Figure 9 The defect testing structure and defect testing method of the semiconductor device are described in detail.

[0089] Figure 8 It is a top view of the defect test structure of the shallow trench isolation region, and the defect test structure includes: a semiconductor substrate (not shown in the figure), an active region 210 on the substrate, and a shallow trench for isolating the insulating active region 210 a trench isolation region 260, the shallow trench isolation region 260 is filled in the corresponding trench 250, Figure 8 The six grooves 250 shown in the figure are arranged in parallel with each other, and the connection line A'-A' at one end of the six grooves 250 intersects the vertical direction B'-B' of the grooves 250, and the included angle is greater than 0 degrees and less than An acute angle of 90 degree...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More