Active area structure

A technology of active area and interconnection structure, applied in the direction of electrical components, electric solid-state devices, circuits, etc., can solve the problem of large leakage current between the source selection gate and the second type of active area, and achieve the compact structure of NAND devices and the area Small, solve the effect of power consumption increase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

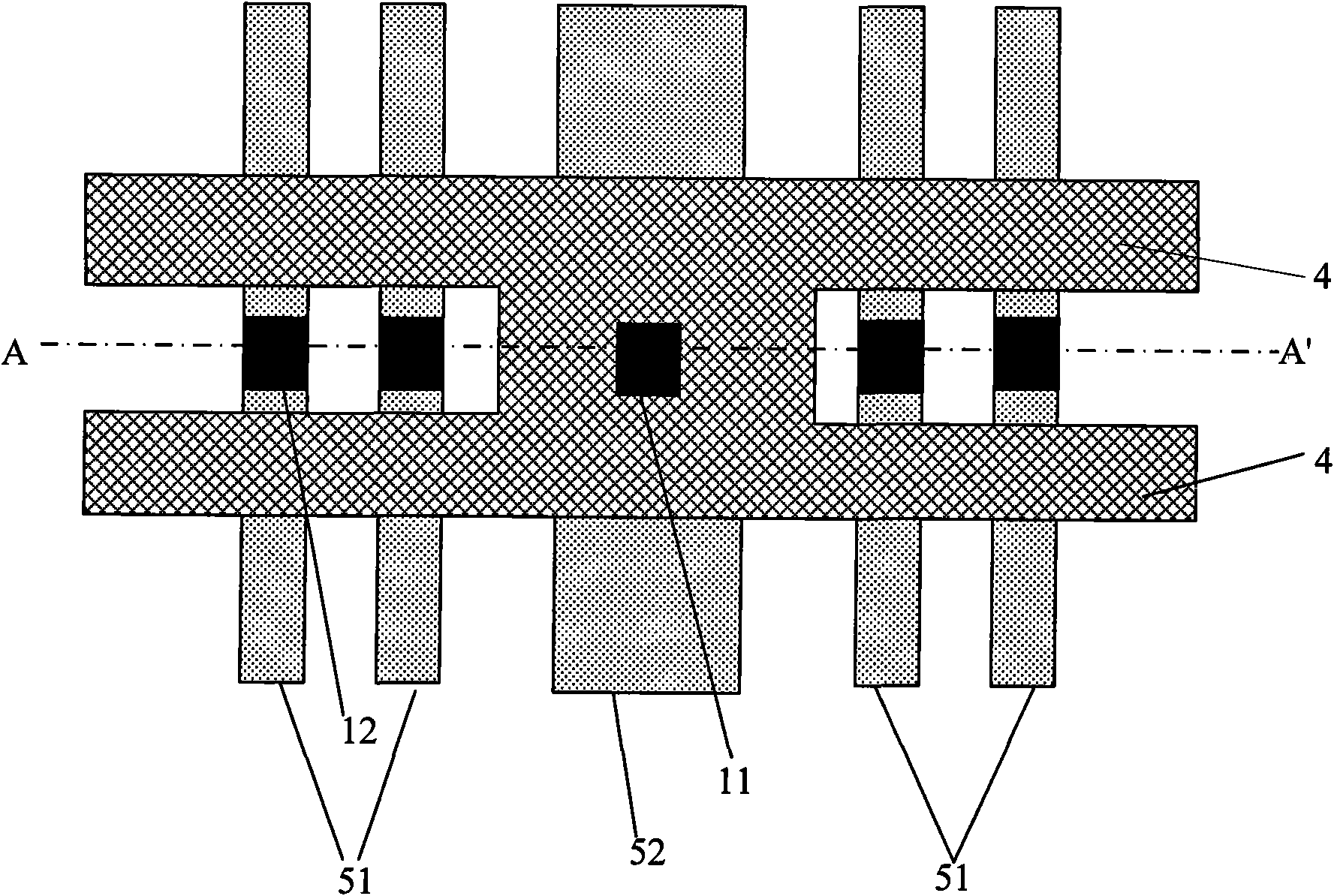

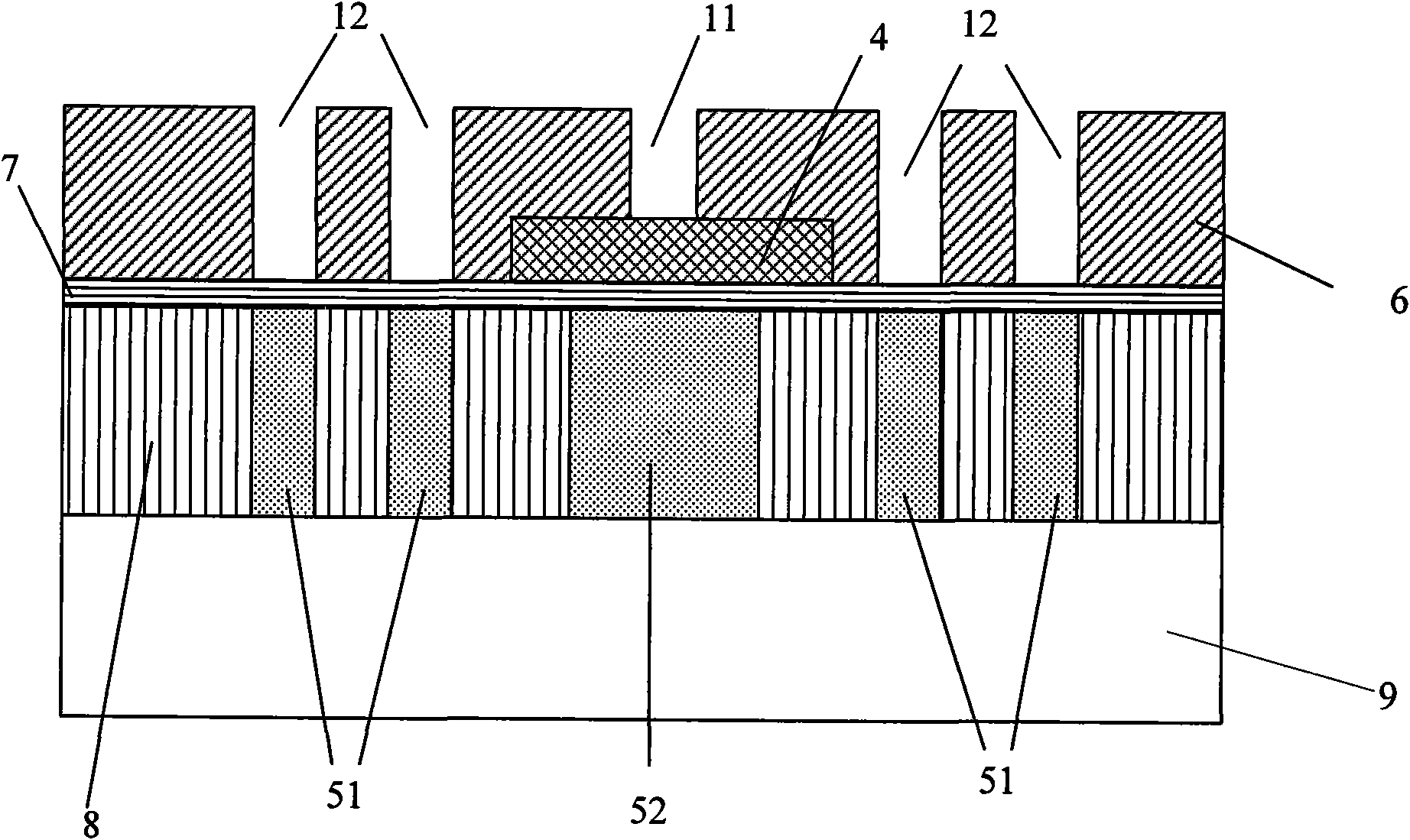

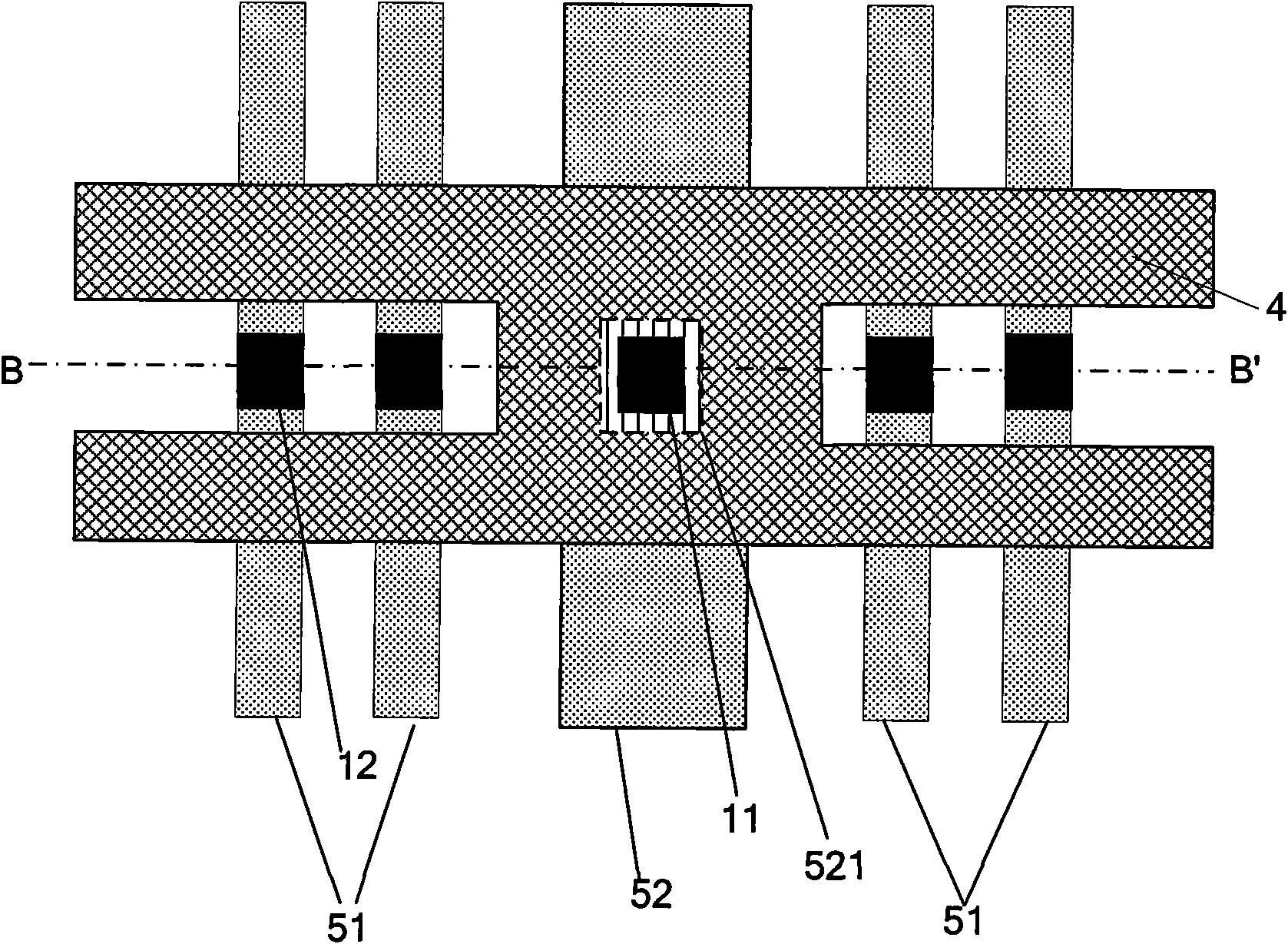

[0016] image 3 It is a partial layout diagram of the NAND device source selection gate in the embodiment of the present invention. From image 3 The layout shown shows active regions within the semiconductor substrate. The active area includes a first type active area and a second type active area. As in the background art, in this embodiment, the first type of active region is the memory cell active region 51 , and the second type of active region is the well lead-out active region 52 as an example. The active selection gate 4 is formed on the memory cell active area 51 and the well extraction active area 52 . An interconnection structure—active region contact hole 12 is formed on the active region 51 of the memory cell. An interconnection structure—source selection gate contact hole 11 is formed on the source selection gate 4 . The active area under the source selection gate contact hole 11 is the well extraction active area 52 . As described in the background, when t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com