Method of producing large gate width silicon carbide metal semiconductor filed-effect transistor (SiC MESFET) with intercellular balance resistors

A technology for balancing resistors and manufacturing methods, applied in resistor manufacturing, resistors, circuits, etc., can solve problems such as low yield, difficult integration, and unstable device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the above objects, features and advantages of the present invention more obvious and understandable, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings and specific implementation methods in the embodiments of the present invention. Obviously, The described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

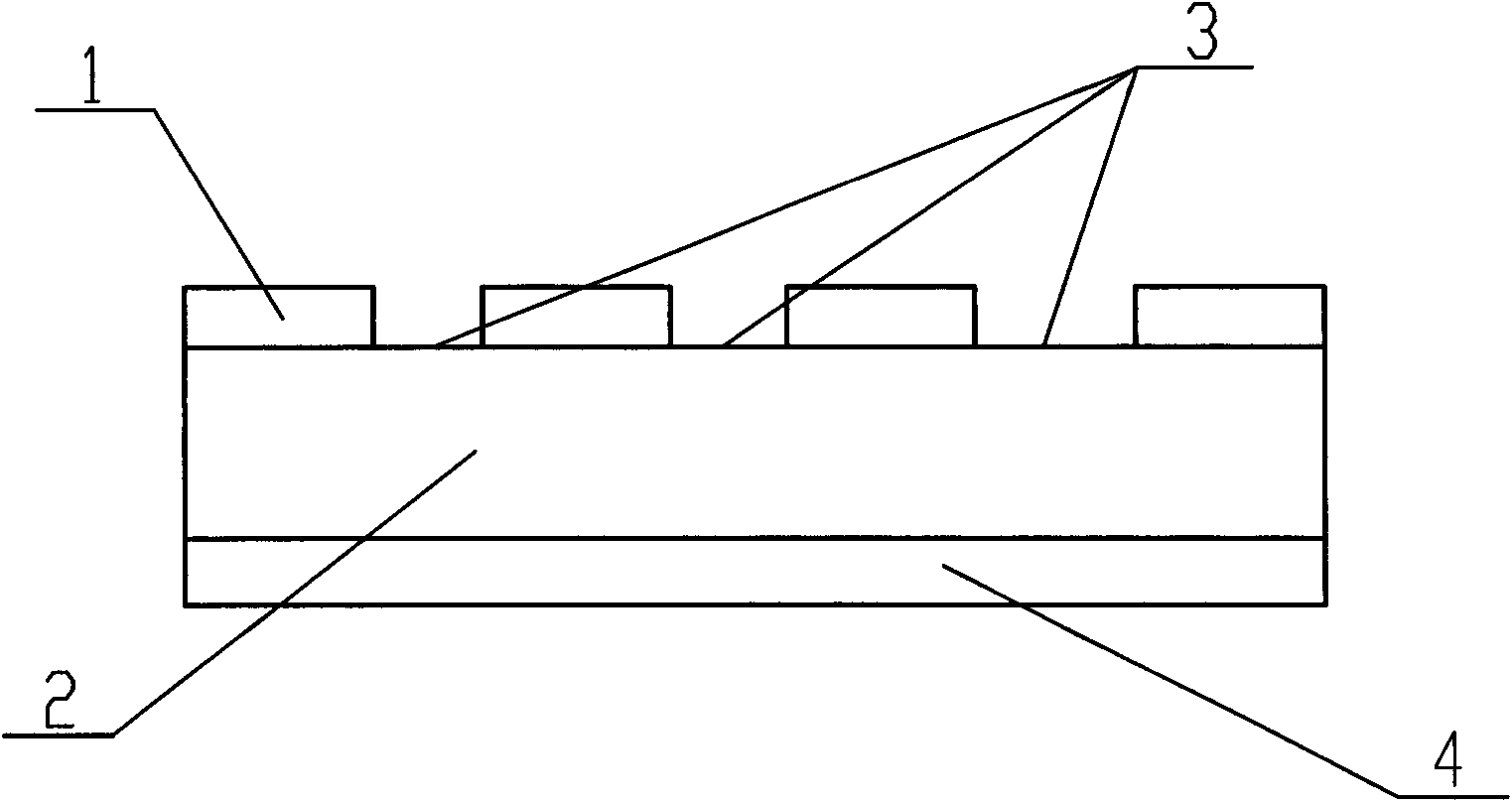

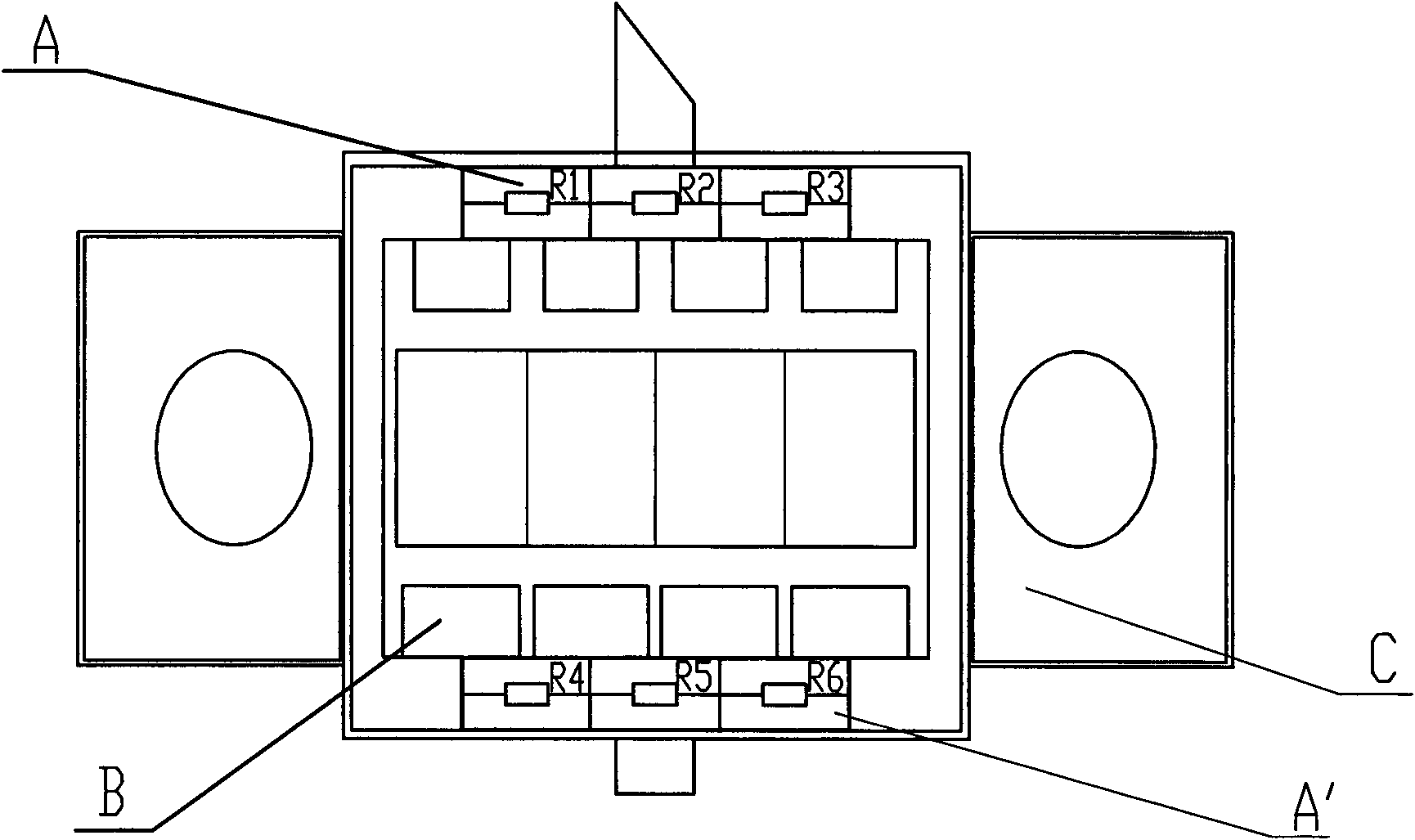

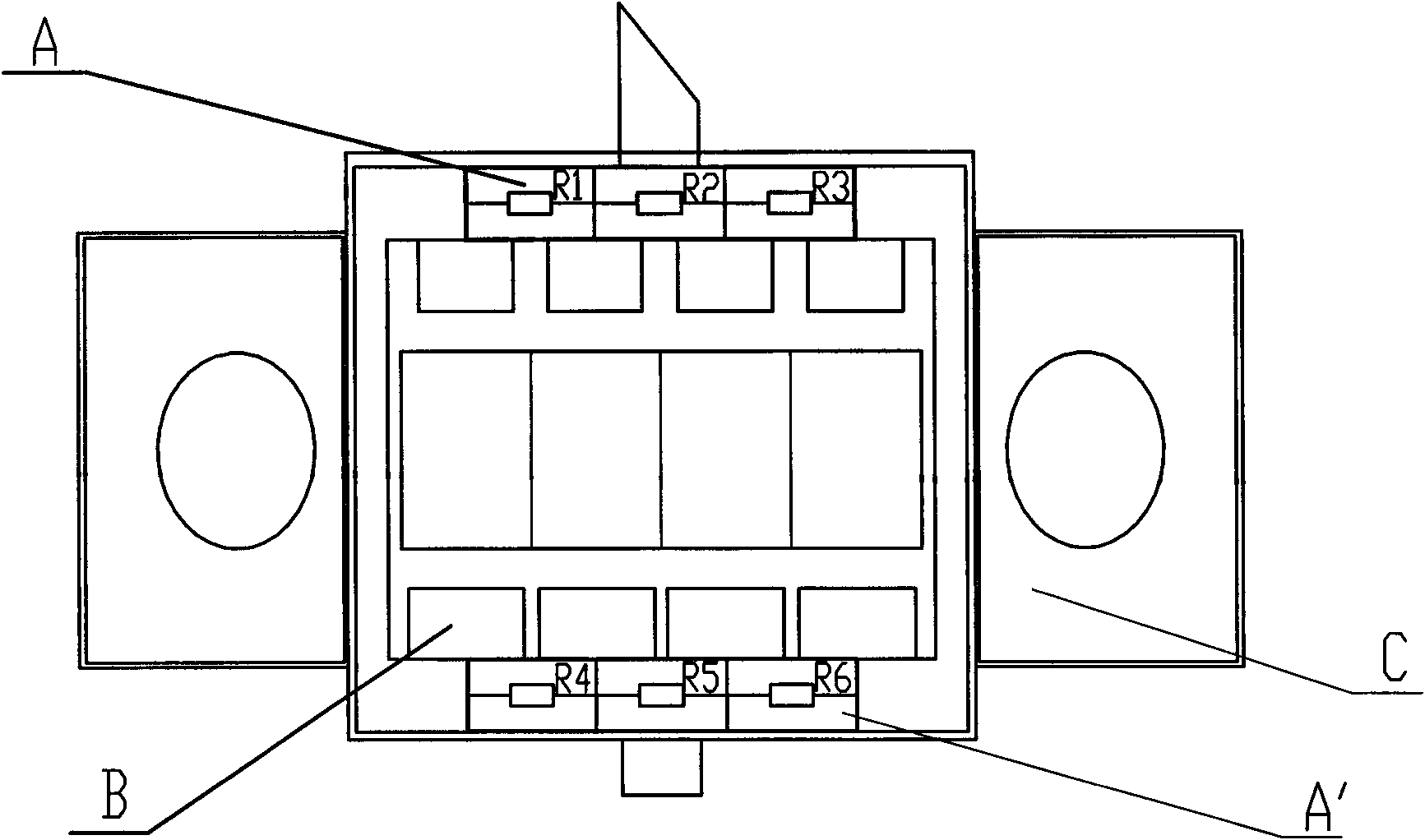

[0024] see figure 1 , The intercellular balance resistance structure described in the large gate width SiC MESFET with intercellular balance resistance includes a dielectric substrate 2 , a bonding wire bonding area 1 , a thin film resistance area 3 and a metal bottom layer 4 on the lower surface. The intercellular balance...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More