Method for detecting random defects of silicon gate of CMOS process

A defect and process technology, which is applied in the field of detecting random defects of CMOS process silicon gate, can solve problems such as increase, short circuit leakage, short circuit or open circuit, etc., and achieve the effect of improving process, increasing yield, and effectively utilizing test structure area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

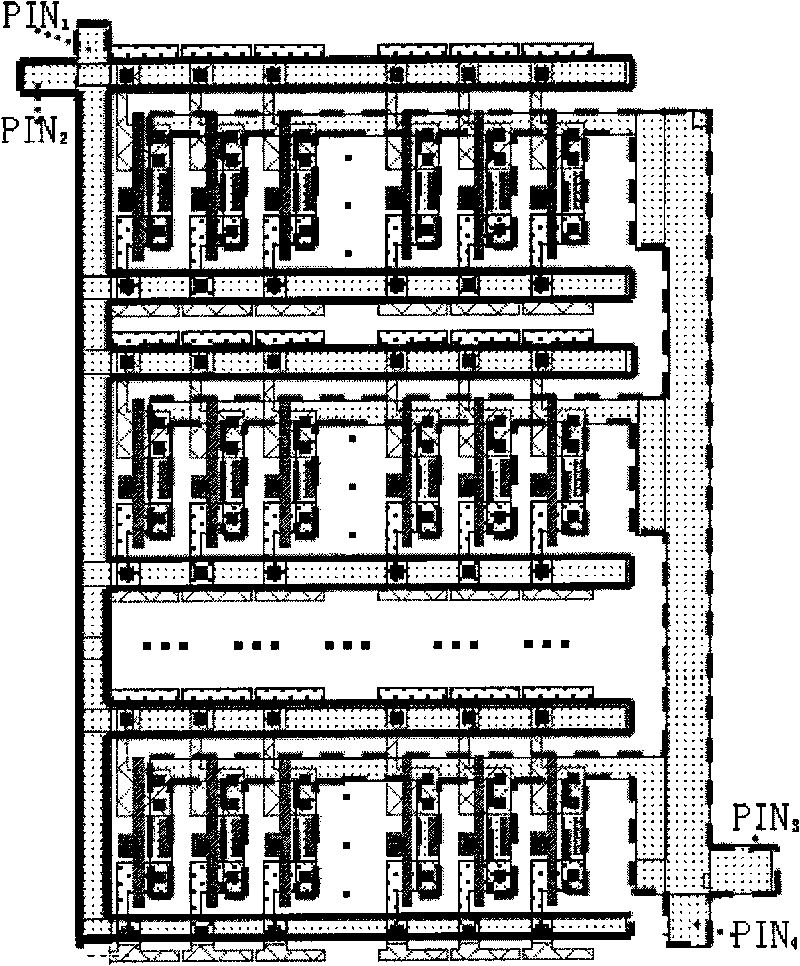

[0027] The present invention will be described in detail below in conjunction with the accompanying drawings.

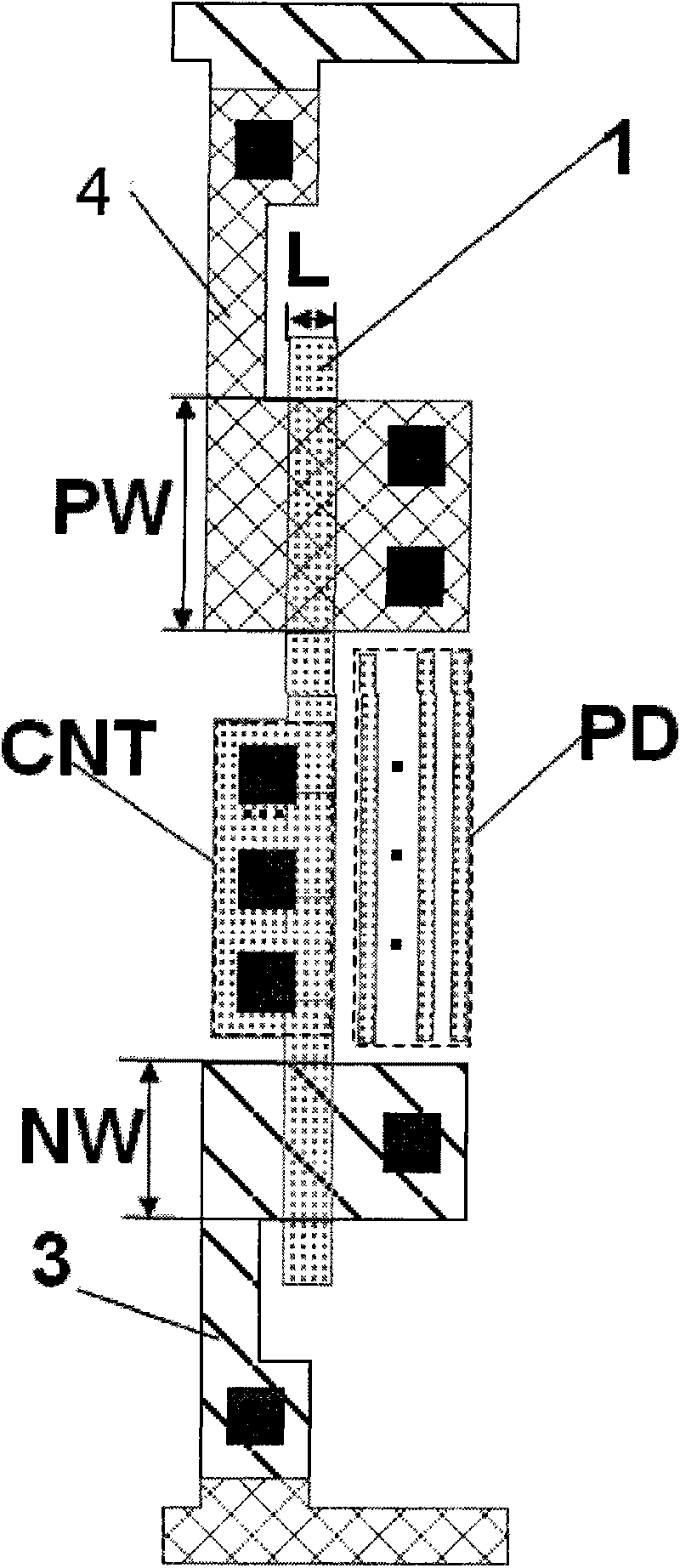

[0028] In order to make the surrounding conditions of the silicon gate of the test structure similar to the actual circuit, this method is based on the typical component transistors and typical standard cell inverters in the CMOS process, and sets the layout parameters that may affect the random defects of the silicon gate as variable parameters. , build the parameterized transistors and parameterized inverters in the array of test structures.

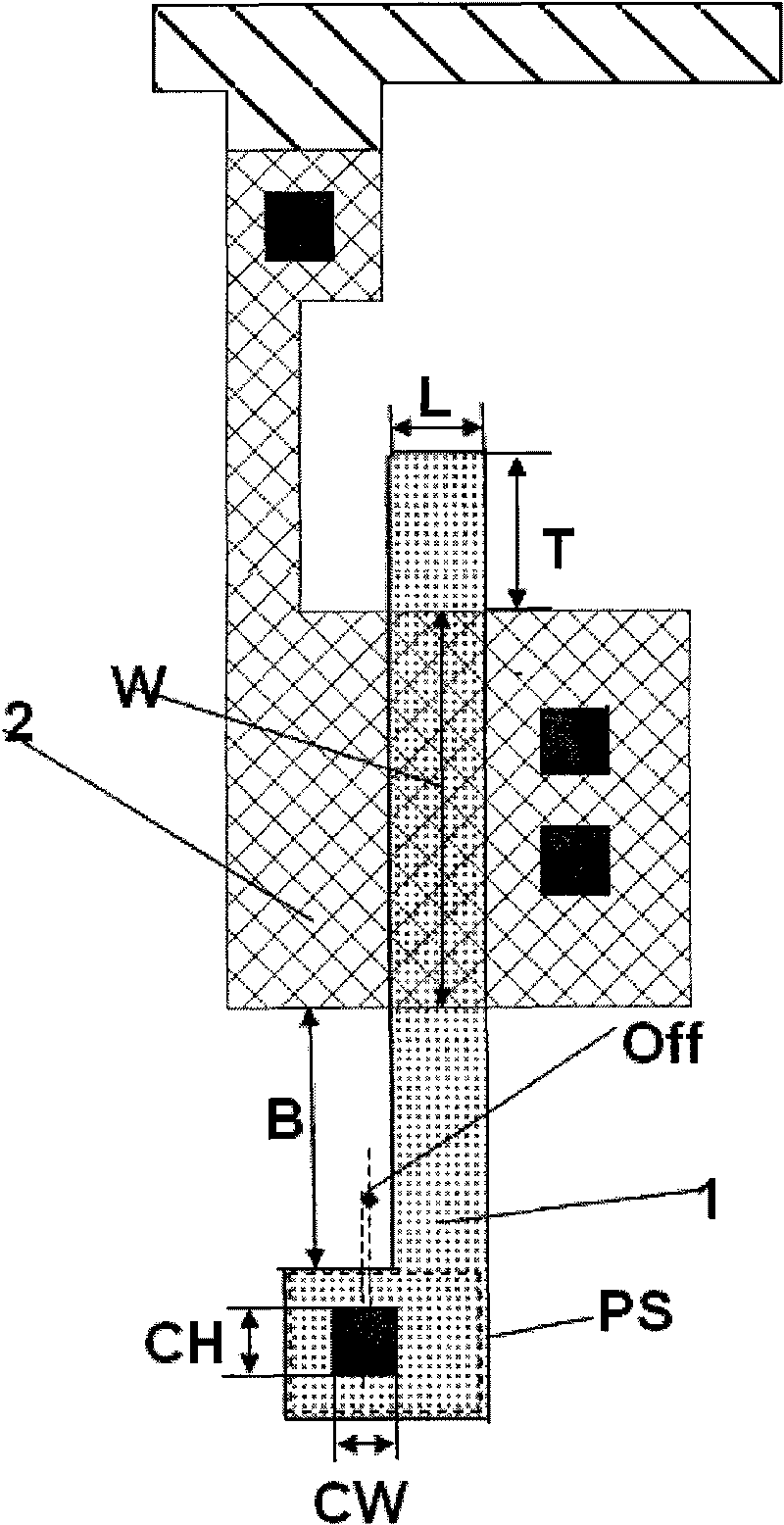

[0029] The CMOS process transistor has a relatively mature structure. This method parameterizes the layout structure that affects the random defects in silicon gate manufacturing. The schematic diagram of the parameterized transistor is as follows figure 1 Shown: T is the distance from the top of the silicon gate 1 to the active region 2, B is the distance from the bottom of the silicon gate 1 to the active region 2, L is the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More