Method for manufacturing semiconductor chip with low warpage

A semiconductor, low warpage technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing the warpage of semiconductor wafers, increasing the cracking of semiconductor wafers, reducing product performance and yield, etc. Effects of increased ductility, reduced stress, low warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

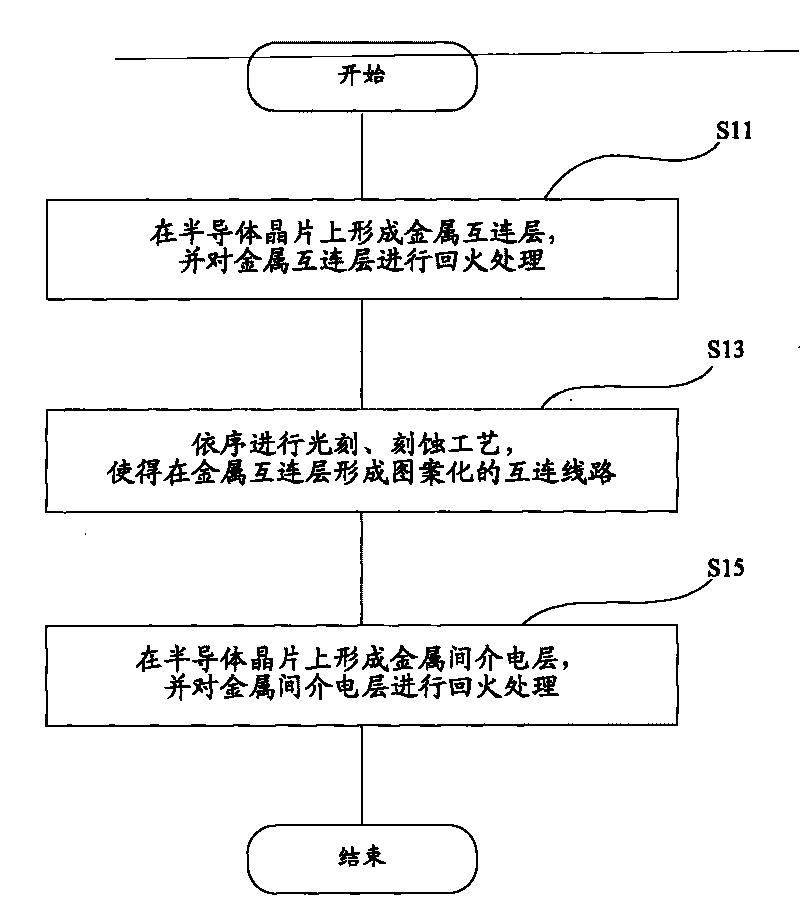

[0025] The embodiment of the present invention preliminarily provides a semiconductor carrier wafer with low warpage. On this basis, at least one tempering step is included in the process of the intermetal dielectric layer and the metal interconnection layer, and the intermetal dielectric layer is fabricated. The oxygen-enriched silicon dioxide deposition process and the FGS deposition process further include controlling the waiting time to reduce the stress of the intermetallic dielectric layer, metal interconnection layer, and semiconductor film in the semiconductor wafer, so that the semiconductor wafer can obtain low The effect of warpage.

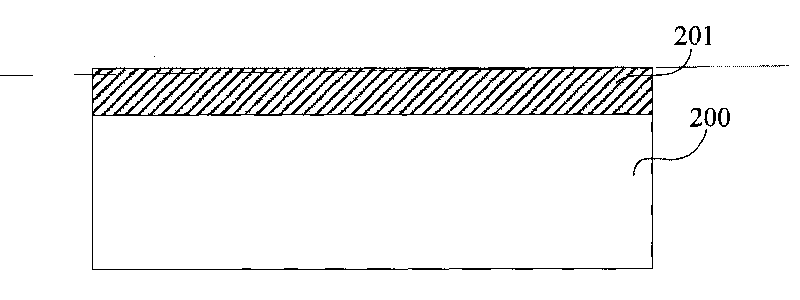

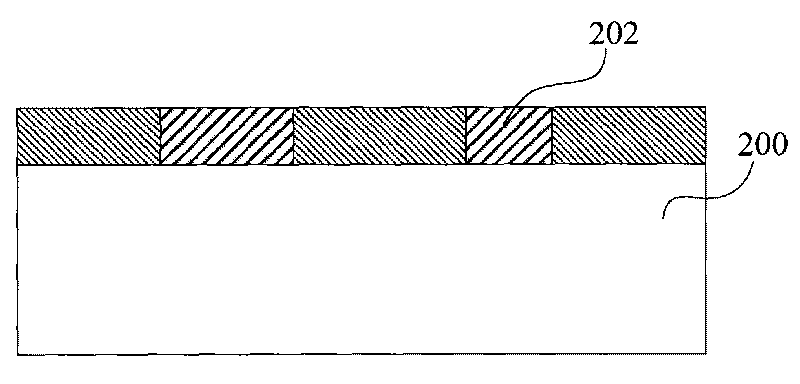

[0026] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0027] The manufacturing method of the semiconductor wafer in the embodiment of the present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More