Electrical inductance in integrated circuit and manufacturing method

A technology of integrated circuits and manufacturing methods, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., and can solve problems such as limited magnetic field strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

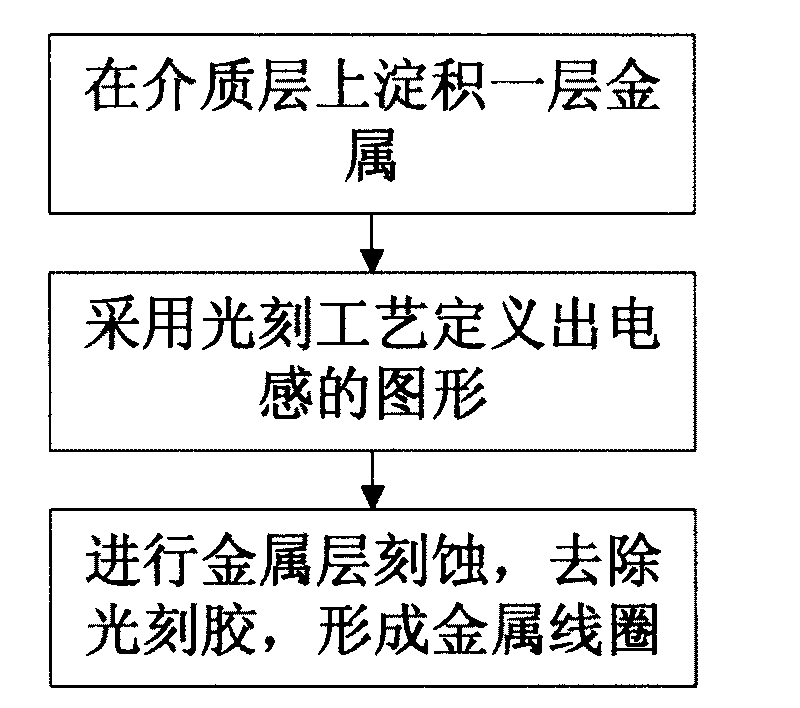

[0031] Such as Figure 6 As shown, the manufacturing method of the inductance in the integrated circuit of the present invention, the whole process all is to finish on silicon substrate, and silicon substrate is not reflected in accompanying drawing, and the present invention comprises the following steps:

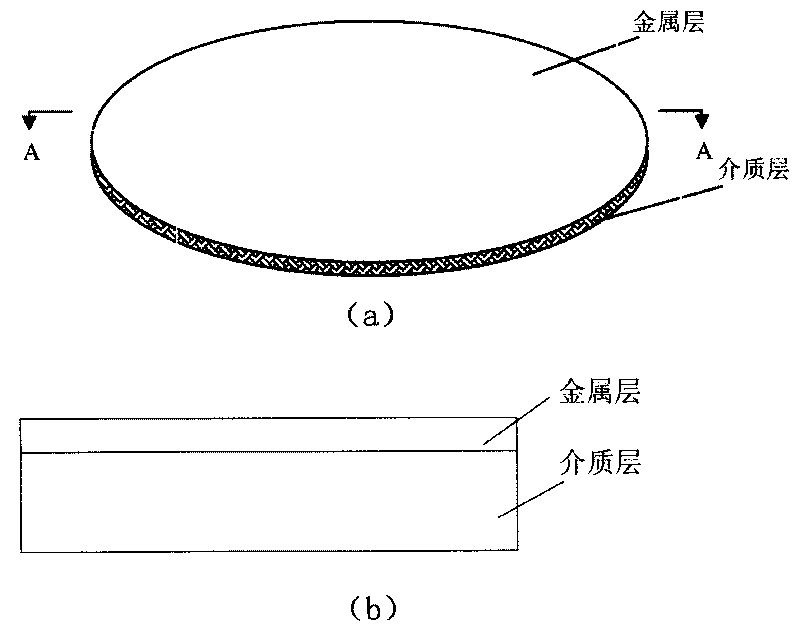

[0032] first step, such as Figure 7 As shown, a layer of metal is deposited on the dielectric layer, generally metal aluminum is used, of course, a metal barrier layer is formed by sputtering before depositing the metal layer.

[0033] The second step, such as Figure 8 As shown, the pattern of the inductor is defined by the photolithography process. That is, apply photoresist on the entire metal layer, and then use a photolithographic mask to perform photolithography. You can use positive photoresist or negative photoresist, and finally develop to form the required inductance. graphics. The inductance pattern here is determined by the layout, and can be a ring formed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com