Method for controlling dynamic direct voltage of parallel connection type active electric filter

A power filter, DC voltage technology, applied in active power filter, harmonic reduction device, AC network to reduce harmonics/ripple, etc., can solve unsolved problems such as DC voltage control, to improve dynamic performance, The effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

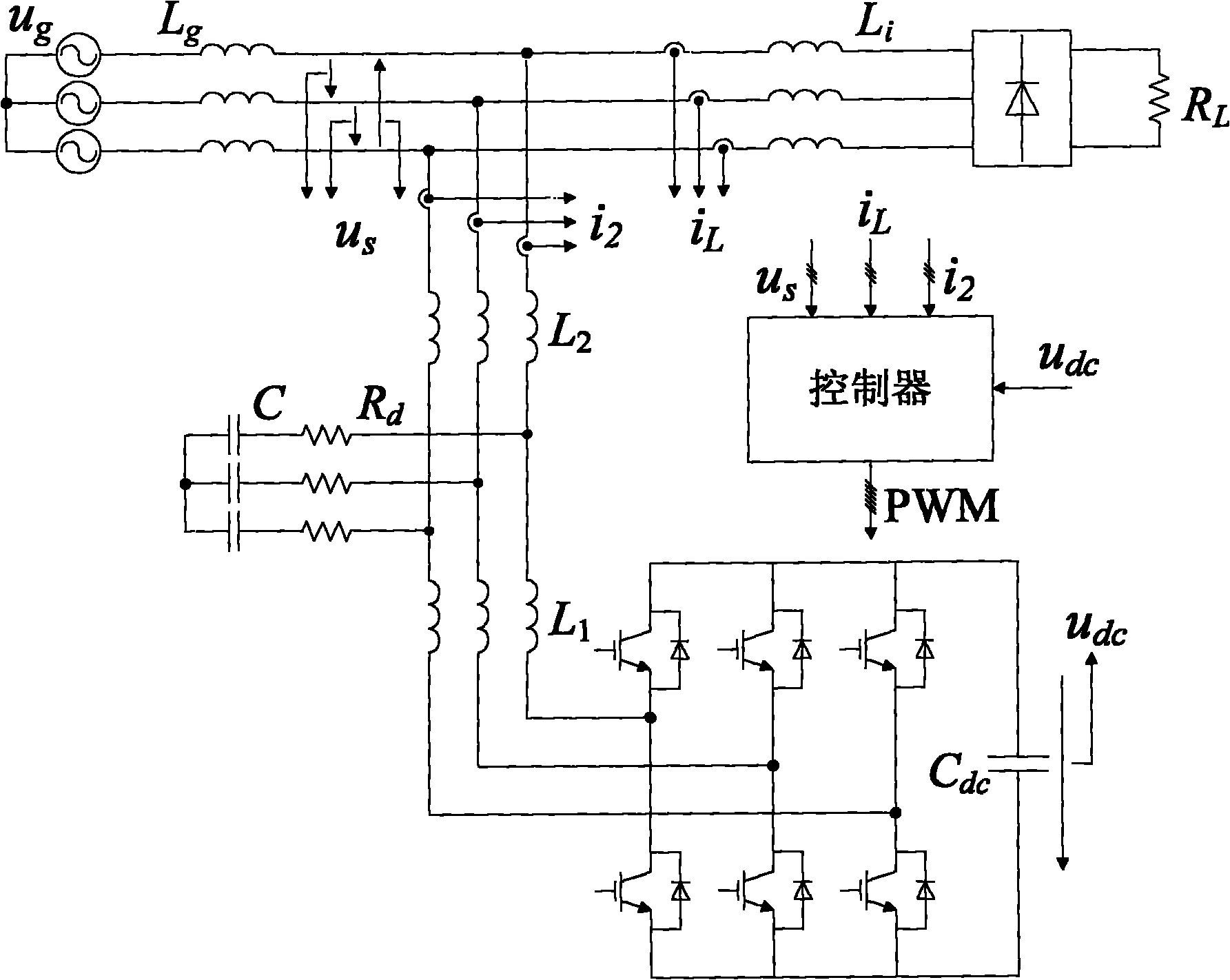

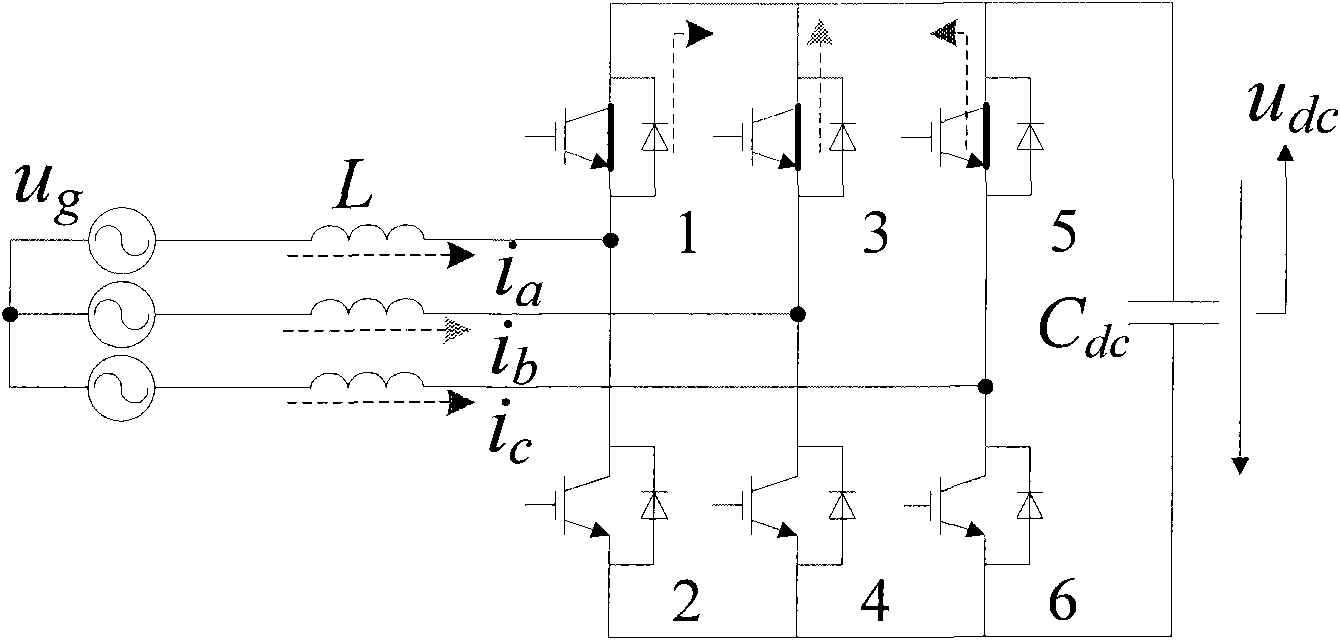

[0049] Embodiment: A method for controlling dynamic DC voltage of a parallel active power filter, characterized in that:

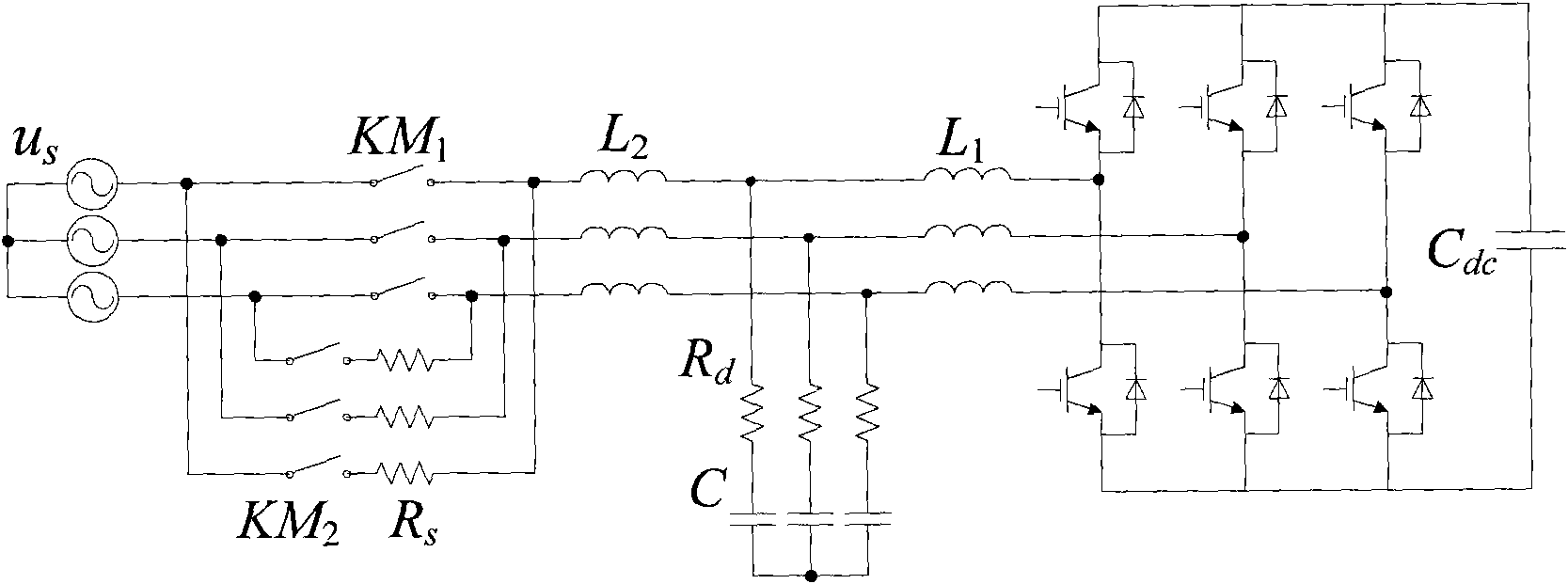

[0050] Step 1, the charging current from the grid precharges the DC side capacitor through the contactor, current limiting resistor, grid side inductance, converter side inductance, and uncontrolled rectifier bridge; this step 1 further includes the following steps: Step 1-1 1. The pre-charging contactor KM2 is closed and the main contactor KM1 is disconnected. Under the action of the grid voltage, the charging current passes through the pre-charging contactor KM2, current limiting resistor, grid-side inductance, converter-side inductance, and uncontrolled rectifier bridge. , and finally flows into the DC capacitor, the DC voltage continues to rise until the charging current is close to zero, and the DC voltage reaches a stable value Udc1; step 1-2, after the charging is stable, the main contactor KM1 is closed, the current limiting resistor Rs and the pre-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More