Single-power clock clocked transmission gate ternary heat insulating circuit and T computing circuit

An adiabatic circuit, transmission gate technology, applied in logic circuits, electrical components, pulse technology, etc., can solve problems such as increased wiring complexity and clock energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

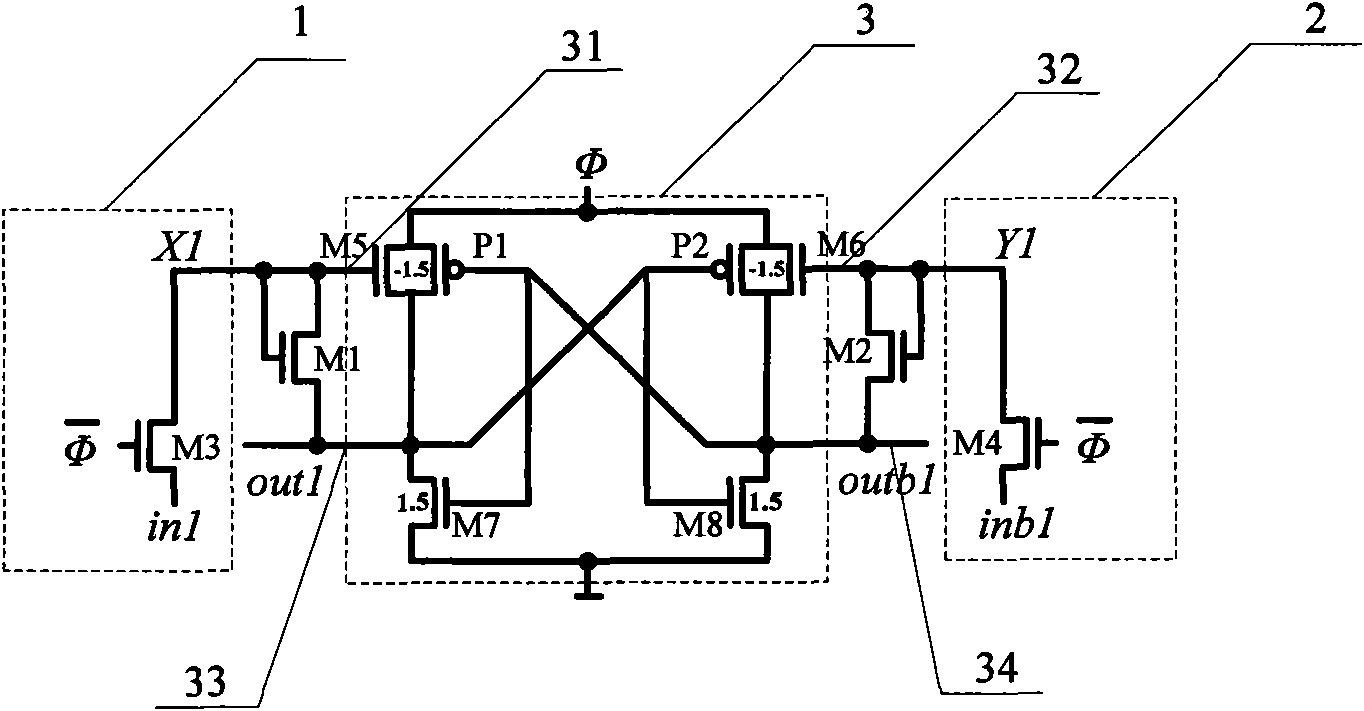

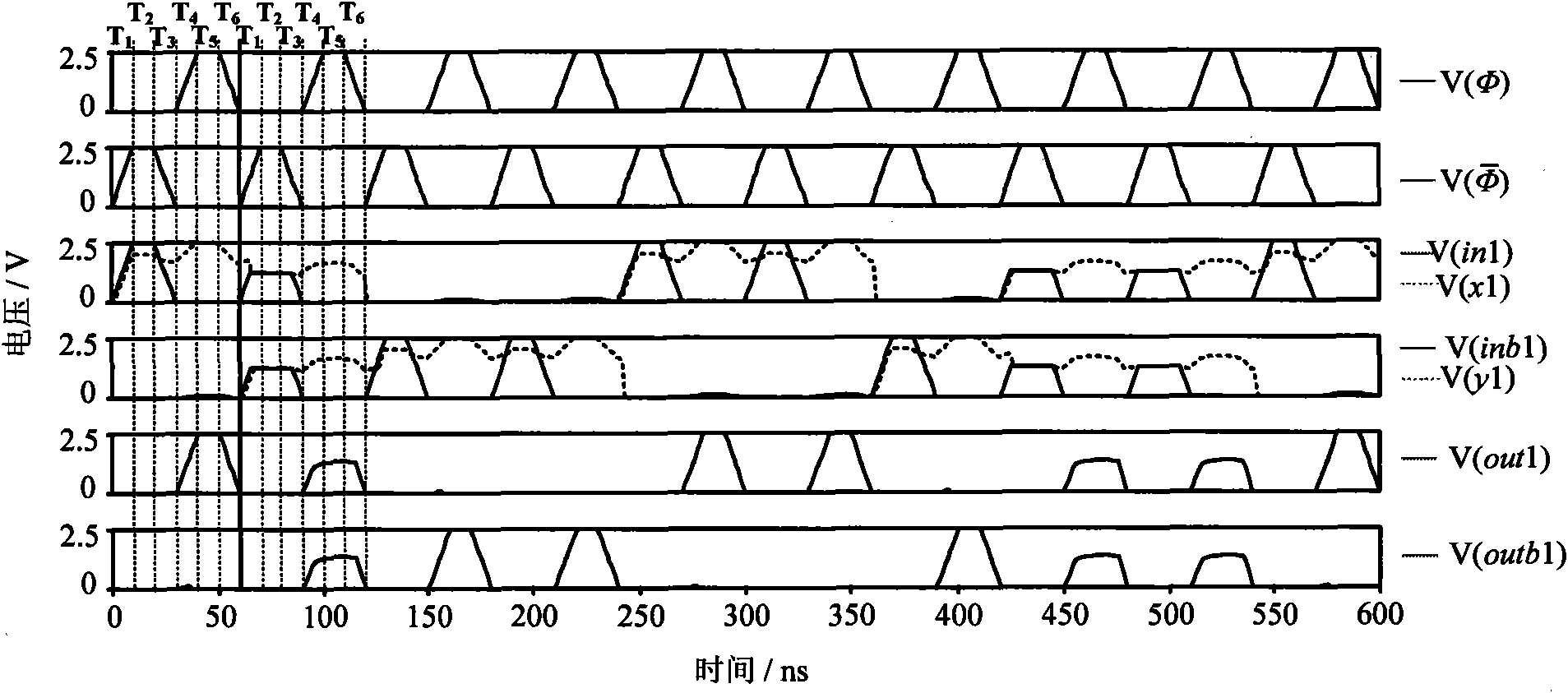

[0031] Based on the research on the adiabatic logic circuit of the binary clock-controlled transmission gate, the present invention proposes a three-valued adiabatic circuit of the single-power clock-controlled transmission gate. The three-valued adiabatic circuit of the transmission gate is divided into two stages of operation: the first stage Level corresponds to the clocked clock signal of logic 2 Under the control, the clocked NMOS transistor is used to complete the sampling of the input signal; the second stage uses the sampled value and the cross storage structure unit to complete the assignment of the output load under the working rhythm of the power clock signal Φ whose amplitude level corresponds to logic 2 And energy recovery, and the output signal and complementary output signal can effectively eliminate the floating. Among them, Φ and The phase difference is 180°, and the amplitudes are all V DD , representing logic 2, in addition to V DD / 2 represents logic 1...

Embodiment 2

[0041] As a multi-valued logical operation operator, T operation constitutes a complete system of multi-valued algebra (T operator algebra), which provides a new way for the research of multi-valued logic theory and application, and can use T operation circuit to construct T operation network to realize Arbitrary multi-valued logic circuit, so the present invention proposes a new T operation circuit clocked by a single power clock.

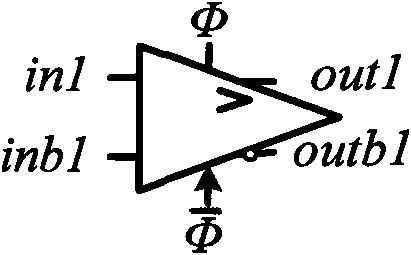

[0042] A kind of single-power clock clocking T operation circuit proposed by the present invention is as follows: Figure 3a As shown, its symbol is as Figure 3b As shown, it is mainly composed of the transmission gate ternary adiabatic circuit 4 and the ternary adiabatic word operation circuit (comprising the first word operation circuit unit 5 and the second word operation circuit unit 6, respectively as shown in the first embodiment) Figure 4a and Figure 4b shown), the ninth NMOS transistor M9, the tenth NMOS transistor M10, the eleventh N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More