Method for improving breakdown voltage of LDMOS devices

A technology of breakdown voltage and devices, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as increased breakdown voltage of devices, achieve the effects of increasing breakdown voltage, increasing process complexity, and saving production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

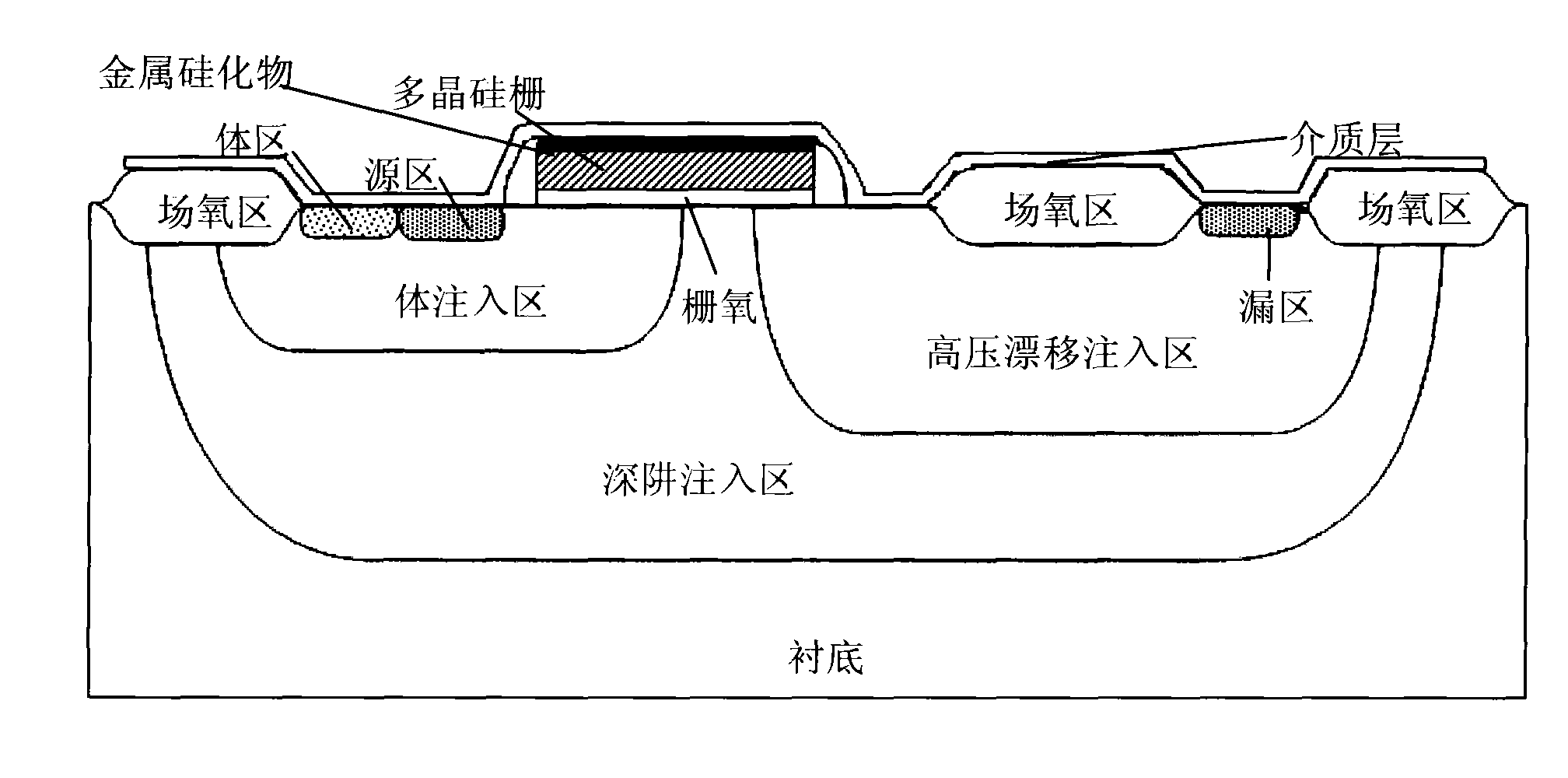

[0016] In the manufacture of semiconductor devices, the preparation process of the main structure of the device is usually called the front-end process, while the metal interconnection between multiple devices in the chip is called the back-end process. The method for improving the breakdown voltage of the LDMOS device of the present invention is mainly divided into two parts:

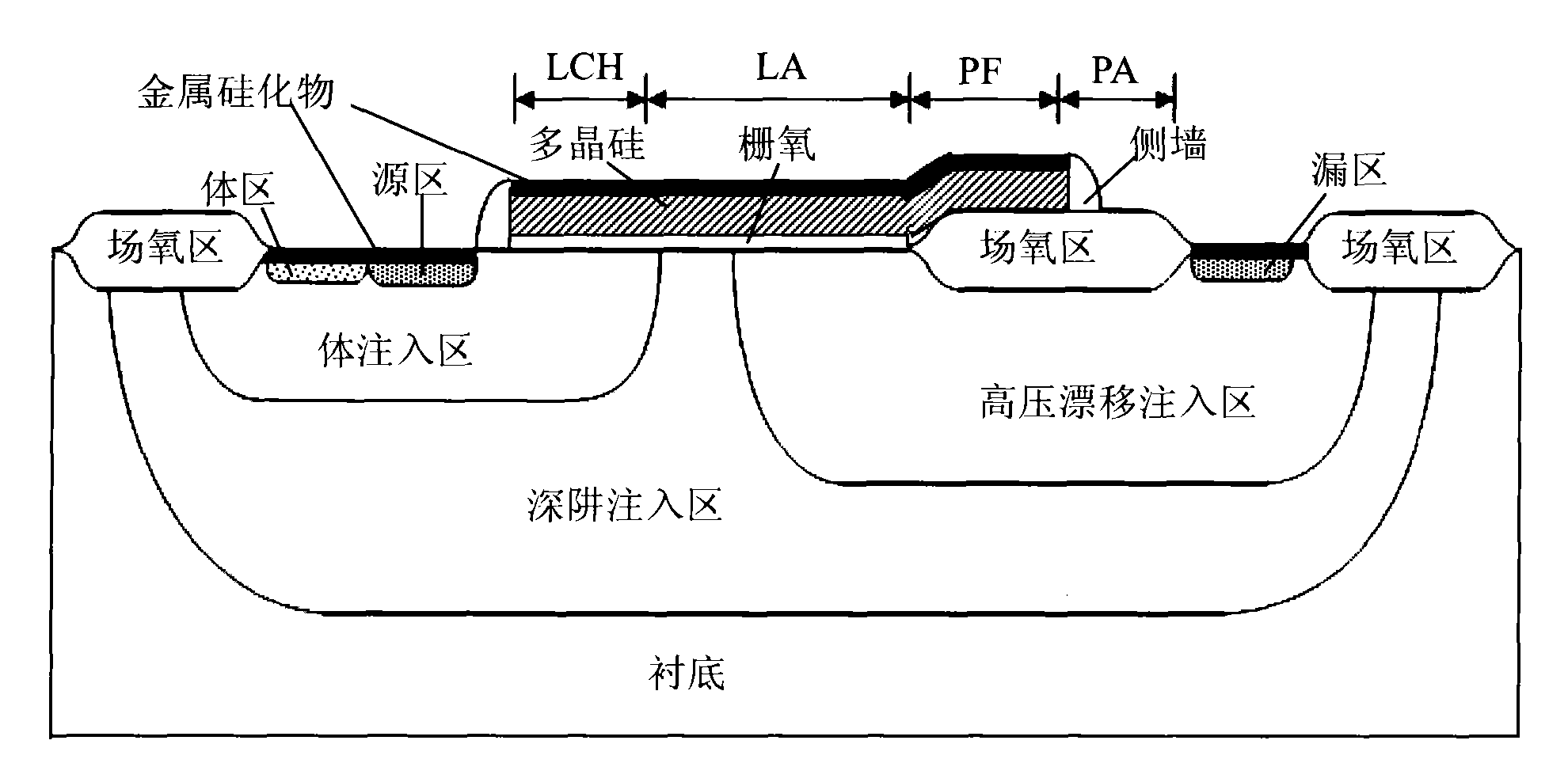

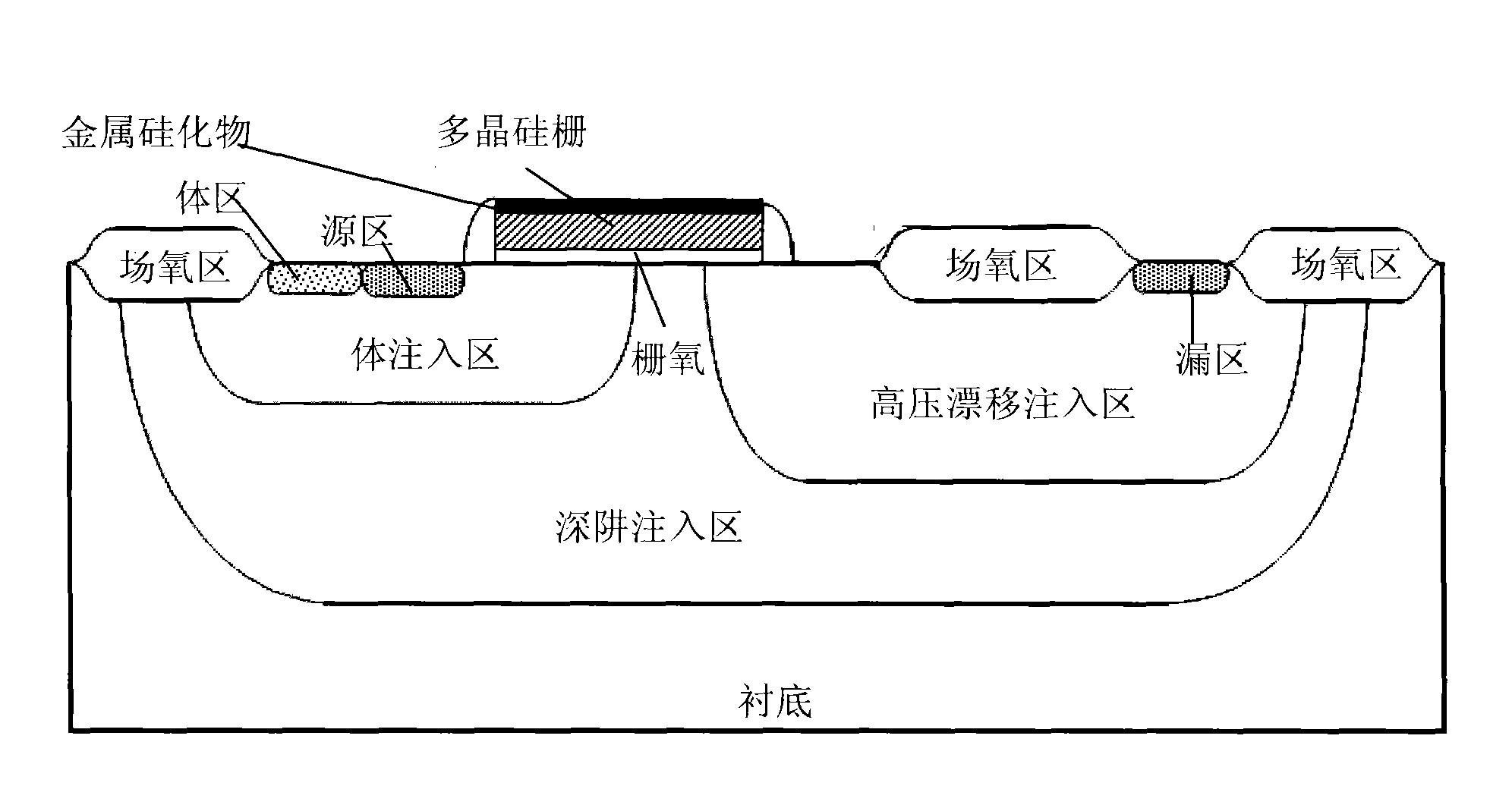

[0017] One is to prepare the gate structure of the LDMOS device in the previous stage according to the conventional method (the gate structure generally includes the underlying gate oxide, the polysilicon gate on the gate oxide, and the sidewalls on both sides of the above two layers of materials), the formed gate The structure is located above the area where the channel is expected to be formed in the LDMOS device and extends above the high-voltage drift injection region, and the gate structure is physically isolated from the field oxygen region located in the high-voltage drift injection region (see ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More