Method for enhancing reliability of chip welding spot, printed circuit board and electronic device

A printed circuit board and enhanced chip technology, which is applied to printed circuits, printed circuits connected with non-printed electrical components, printed circuits assembled with electrical components, etc., can solve the problem of reducing manufacturing efficiency, increasing equipment cost investment, and increasing process flow and other issues, to achieve the effect of improving manufacturing efficiency, reducing equipment cost investment, and reducing process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

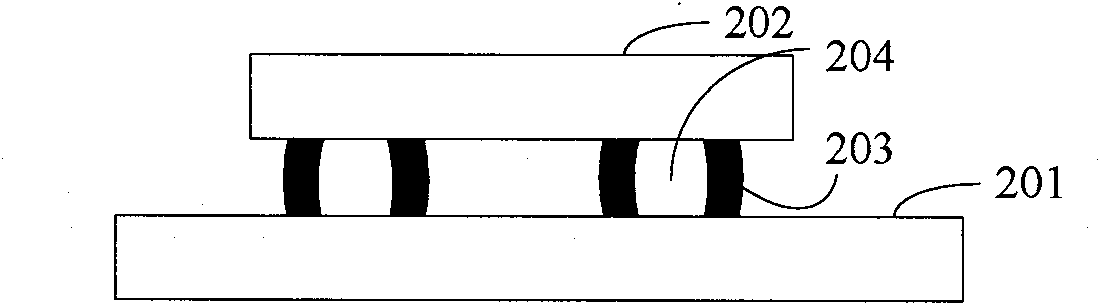

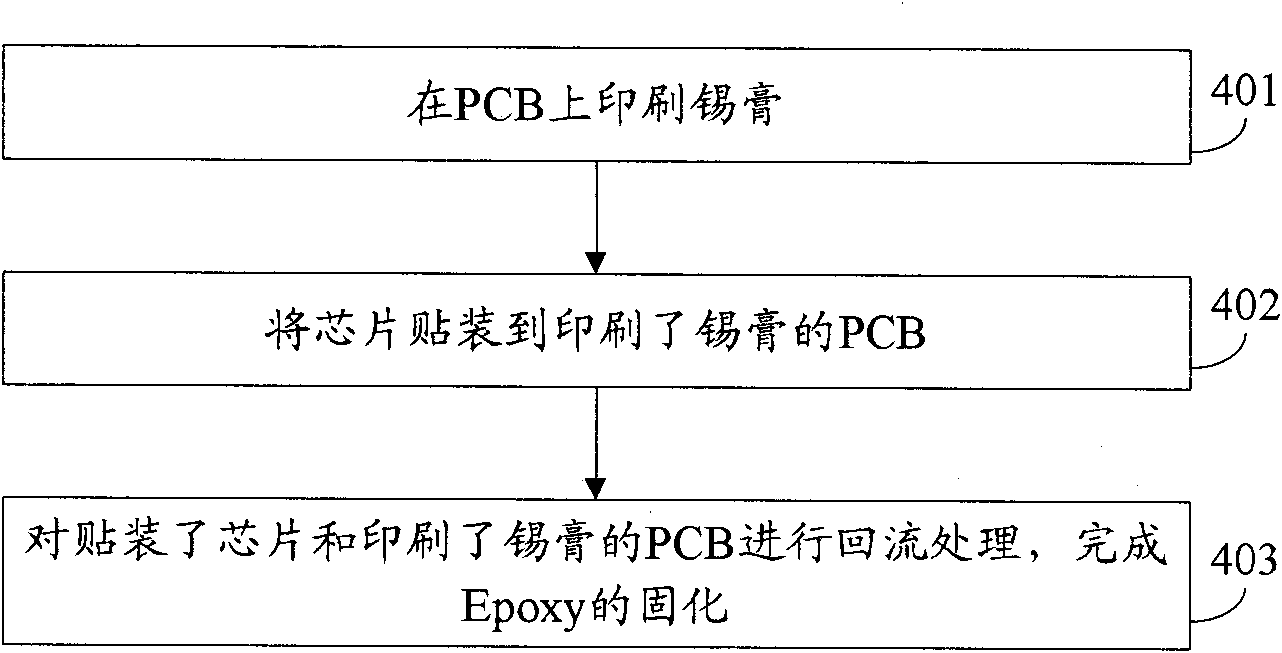

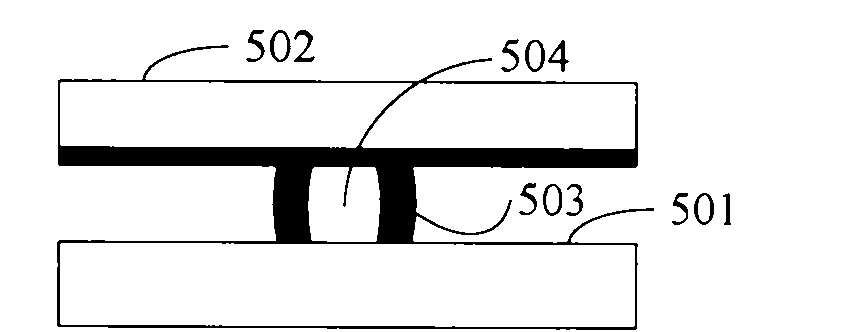

[0029] First introduce the method for enhancing the reliability of chip solder joints provided by the embodiment of the present invention, figure 1 The process flow of the method for enhancing the reliability of chip solder joints provided by an embodiment of the present invention is described. This embodiment describes the process of enhancing the reliability of top-layer chip solder joints in the process flow of POP, including:

[0030] 101. Dip Epoxy Flux onto t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More