Packaging structure

A technology of packaging structure and packaging area, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of lead frame collision, affecting the yield of semiconductor packaging process, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

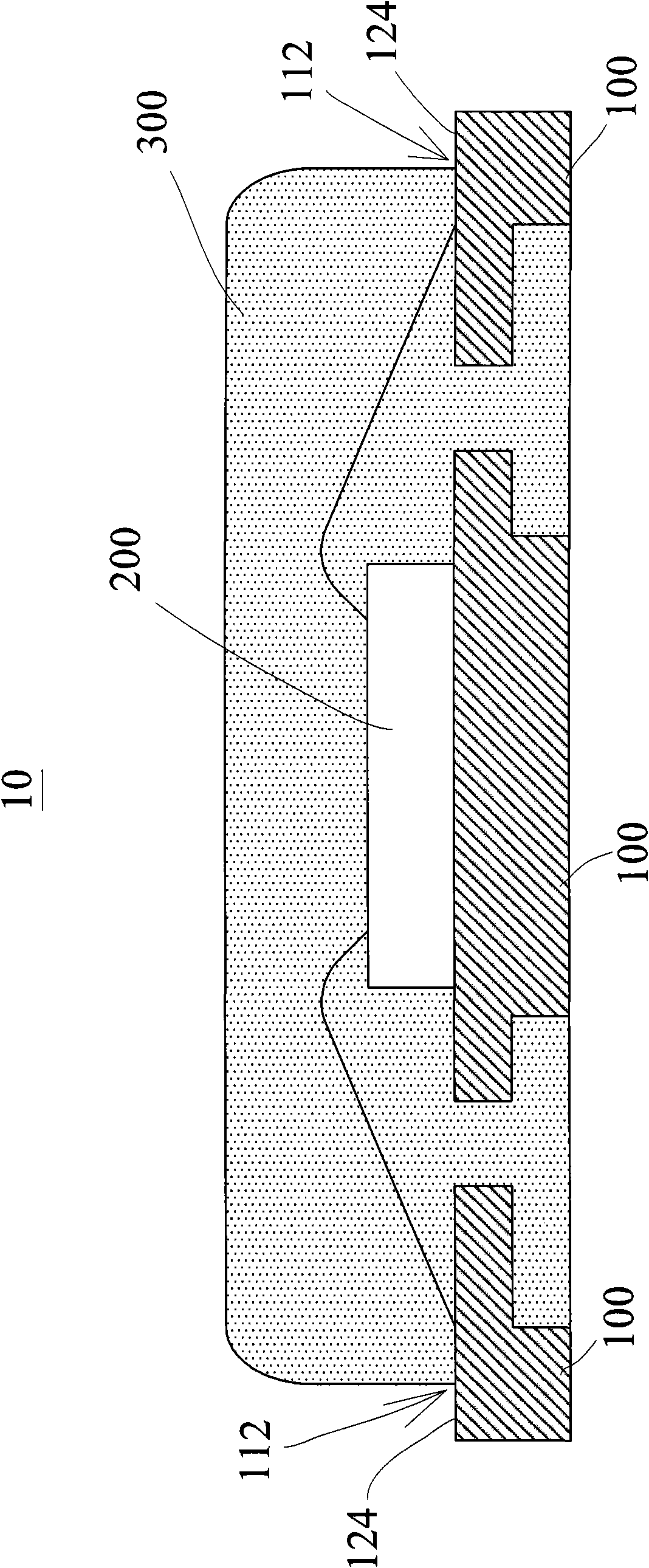

[0028] One embodiment of the present invention is a packaging structure 10 applied in a semiconductor packaging process. see figure 1 , which is a schematic partial cross-sectional view of a single package on the package structure 10 . The package includes: a lead frame 100 , a chip 200 and a molding compound 300 . As shown in the figure, the chip 200 is placed on the lead frame 100 and electrically connected to the lead frame 100 by bonding; in other implementations, the chip 200 can also be electrically connected to the lead frame 100 by other means. The molding compound 300 molds and covers the chip 200 on the lead frame 100 . In this embodiment, the lead frame 100 is applied to a Quad Flat No lead (QFN) package structure. In other implementations, those skilled in the art can easily deduce the application of other package structures. .

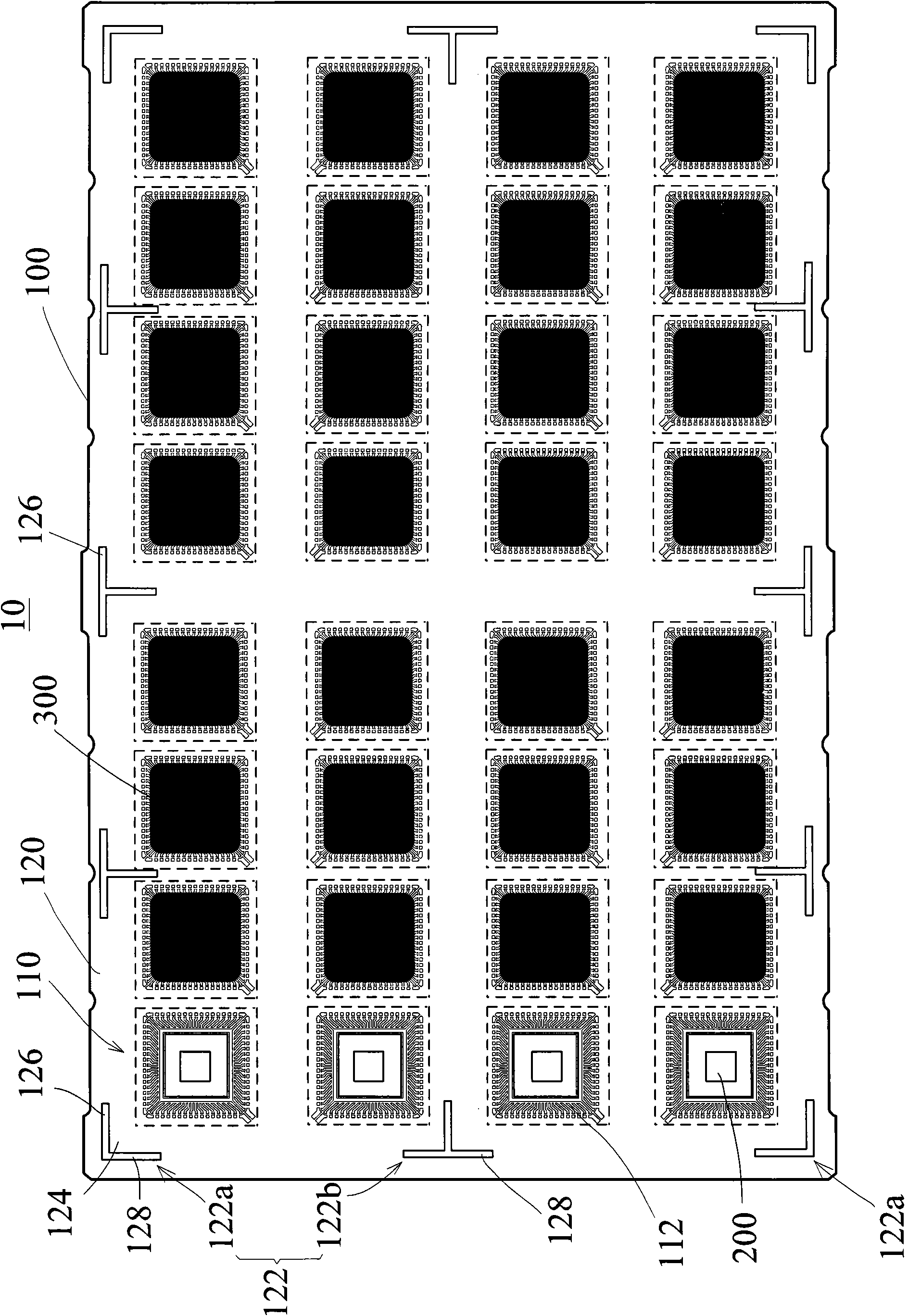

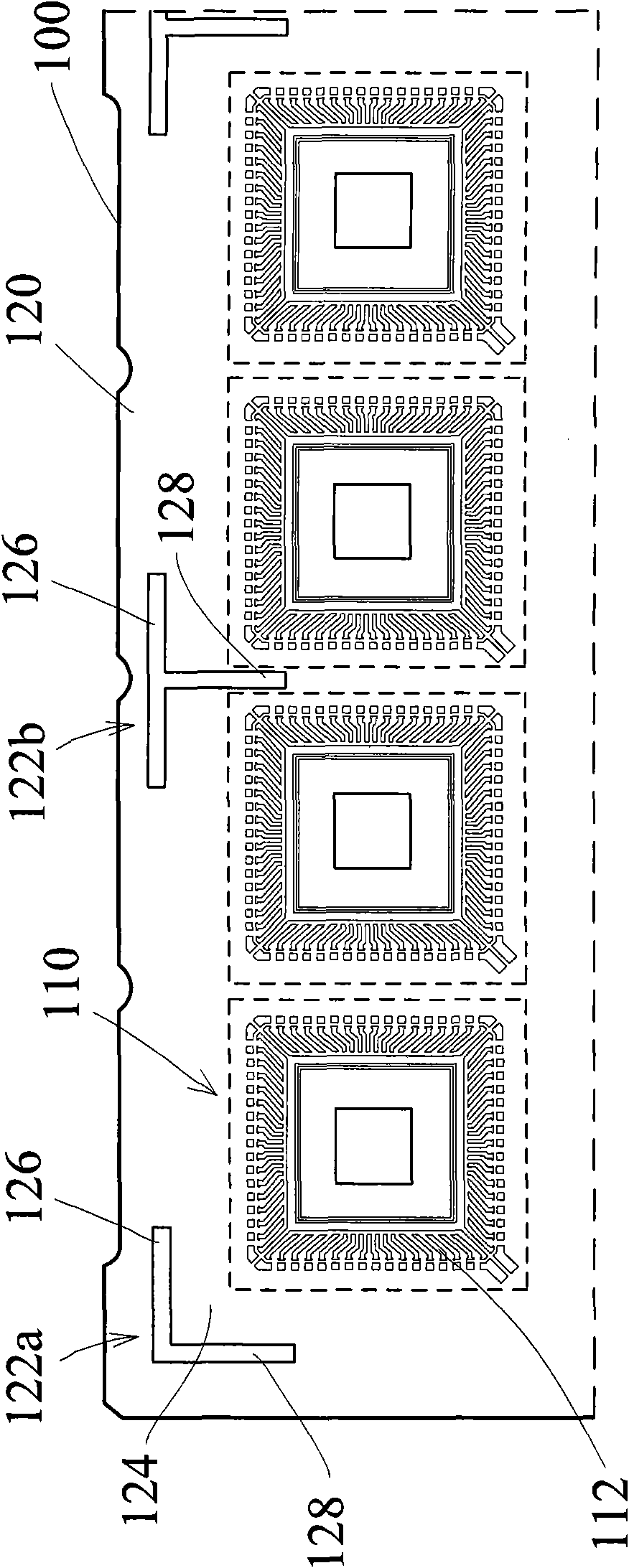

[0029] Please continue to refer to figure 2 and image 3 , the lead frame 100 of the package structure 10 has a plurality of packa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com