Super Junction VDMOS device

A device and electrode technology, which is applied in the field of Super Junction VDMOS devices and power semiconductor devices, can solve the problems of increasing device manufacturing costs, device leakage current, and device on-resistance, and achieve improved heat dissipation performance, small device size, and reduced The effect of device contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

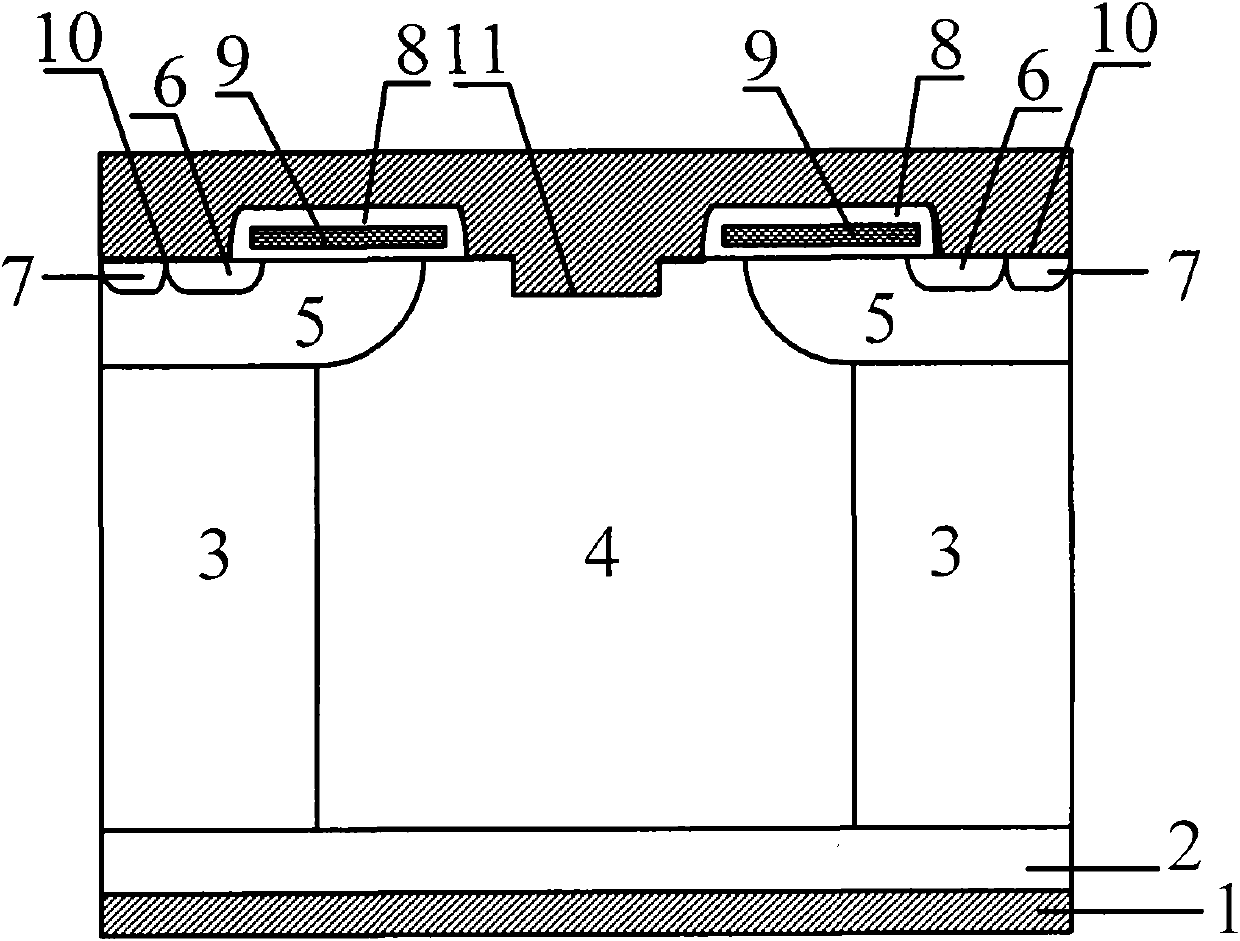

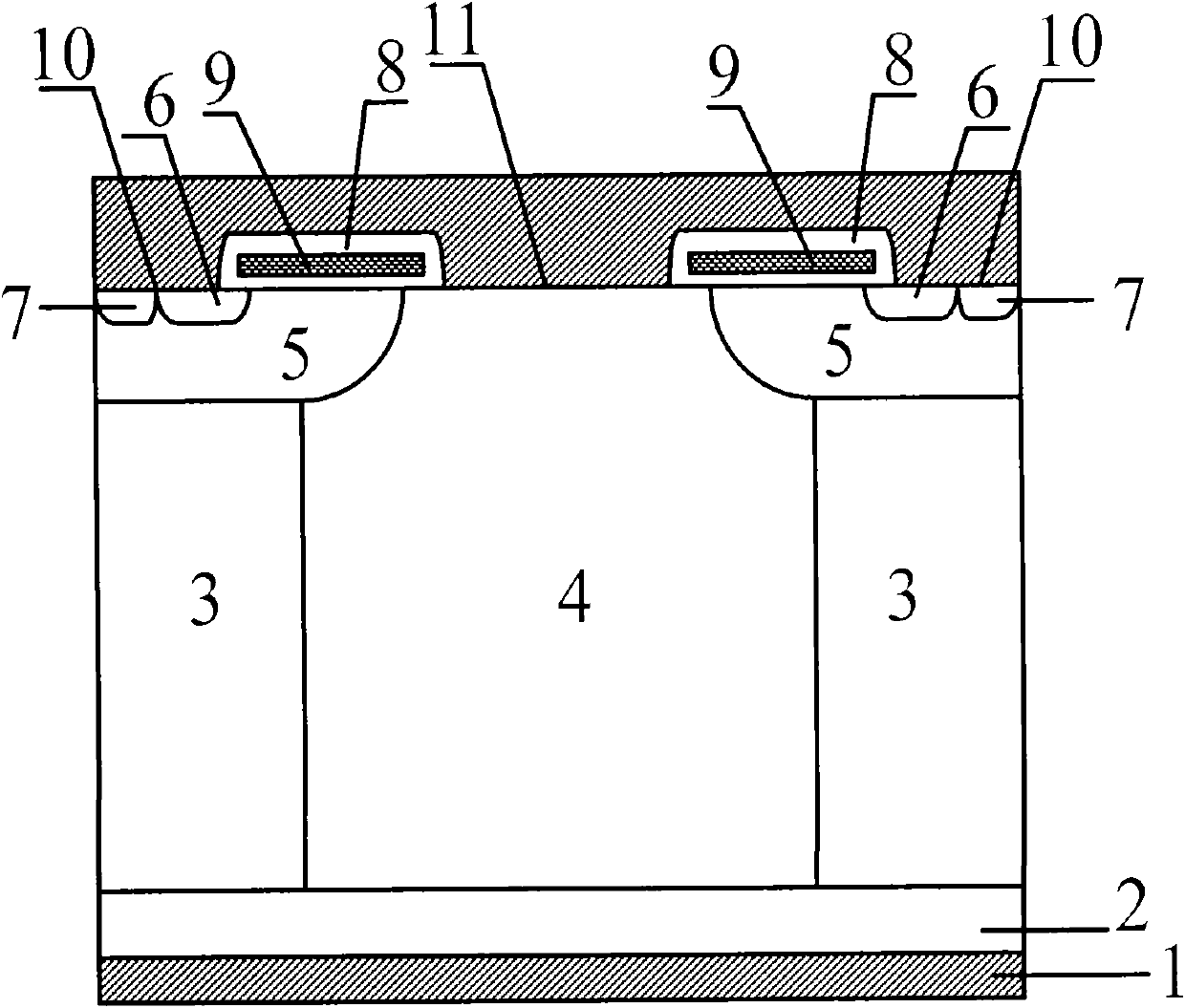

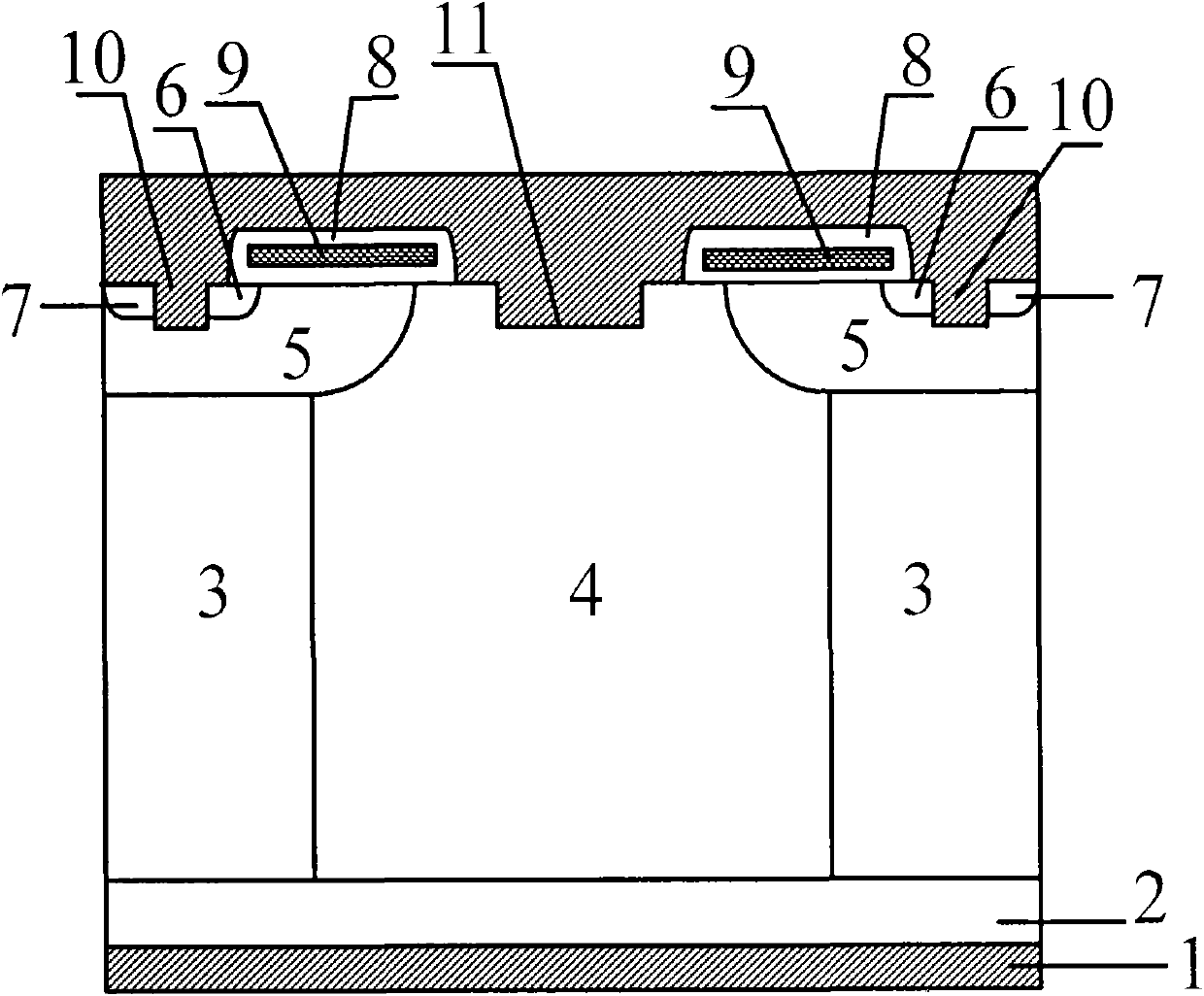

[0023] A Super Junction VDMOS device, such as image 3 shown, including N + Substrate 2, located at N + The metal drain 1 on the back surface of the substrate 2 is located at N + The Super Junction structure on the surface of the substrate 2 , the polysilicon gate electrode 9 and the metal source electrode 10 . The Super Junction structure is formed by sandwiching an N-type column area 4 between two P-type column areas 3 . There is a P-type base region 5 on both sides of the top of the Super Junction structure, and the P-type base region 5 is in contact with the P-type column region 3 and the N-type column region 4 respectively; the two P-type base regions 5 have N + source region 6 and P + body area 7. The polysilicon gate electrode 9 is located above the P-type base region 5 and the N-type pillar region 4 , and is insulated from the P-type base region 5 and the N-type pillar region 4 by a gate oxide layer. The metal source electrode 10 is located on the uppermost layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More