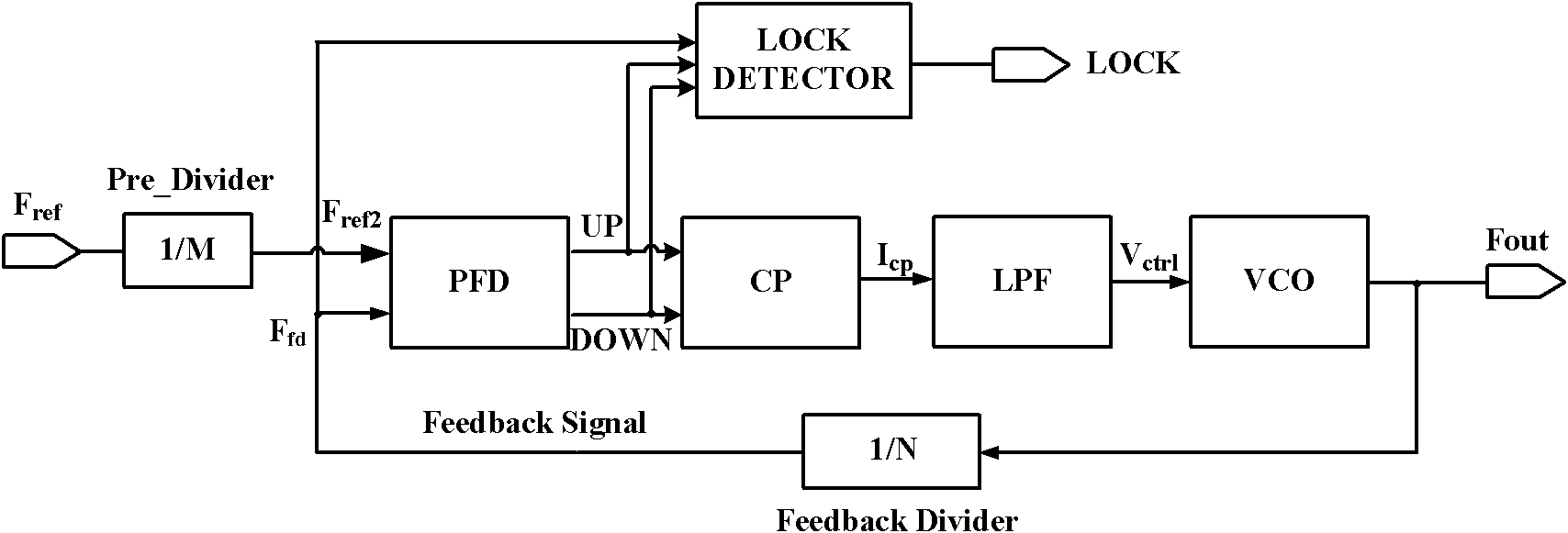

Locked detection circuit applied to phase locked loop (PLL) with dynamic reconfigurable frequency dividing ratio

A technology of lock detection and frequency division ratio, applied in the direction of electrical components, automatic power control, etc., can solve the problems of unable to detect the locked state of the phase-locked loop in time, the feedback clock signal is unstable, the output clock signal is unstable, etc., to achieve The effect of increasing complexity, simple structure and excellent performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

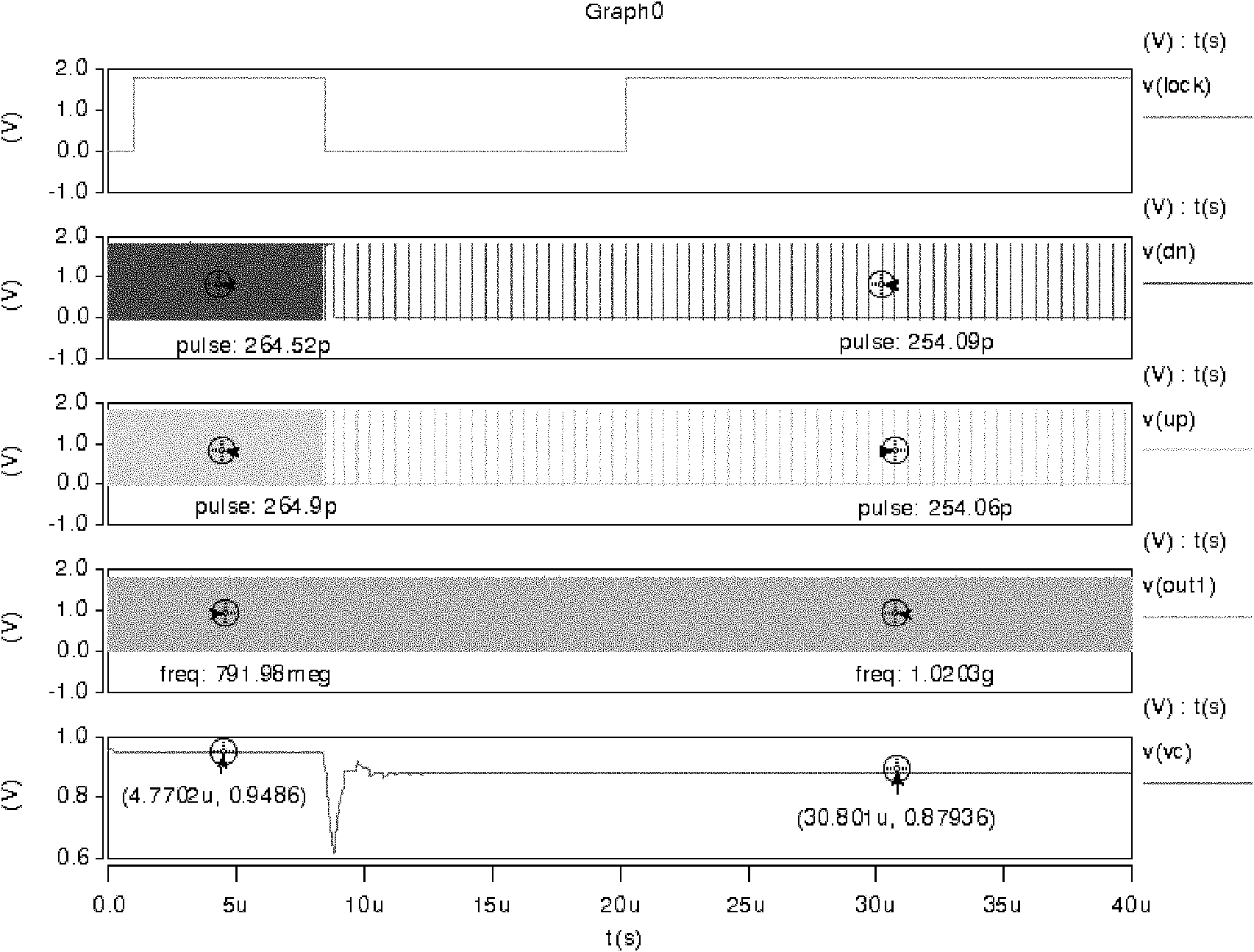

Examples

Embodiment Construction

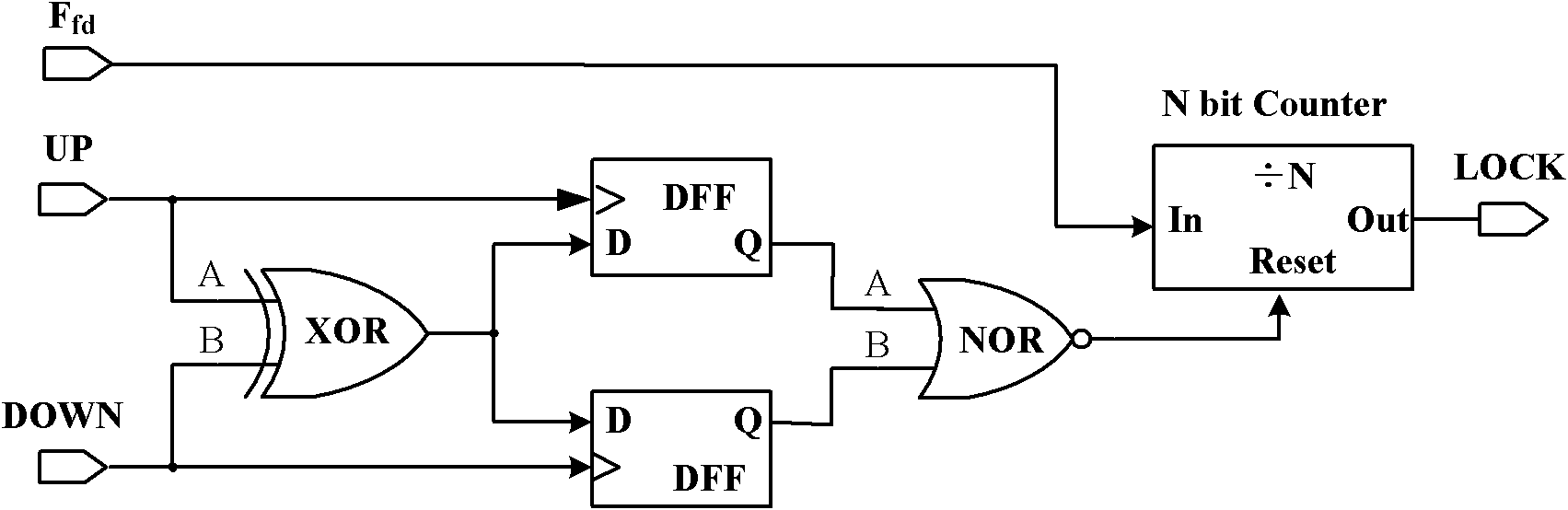

[0012] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0013] Such as figure 2 As shown, the lock detection circuit of the present invention applied to a PLL with a dynamically reconfigurable frequency division ratio includes an exclusive OR gate unit (X1), two D flip-flop units (D1, D2), a NOR gate unit ( N1) and an N-bit counter unit (C1), the lock detection circuit applied to the PLL with a dynamically reconfigurable frequency division ratio uses the exclusive OR gate unit X1 as the input stage, and the two input terminals of the exclusive OR gate unit X1 (A, B) are the UP and DOWN signals output by the phase frequency detector (PFD), the output is connected to the D terminals of the two D flip-flop units (D1, D2), and the D1 and D2 units use the UP and DOWN signals as D The clock of the flip-flop samples the data output by the XOR gate unit X1. The output of the D1 and D2 units is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More