Semiconductor memory device

A storage device and semiconductor technology, applied in information storage, static memory, digital memory information, etc., can solve problems such as long pre-charging time, and achieve the effect of preventing malfunction, realizing action, and stabilizing action

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Here, the same symbols are assigned to the same parts in the configuration of the IO module, and repeated explanations are omitted.

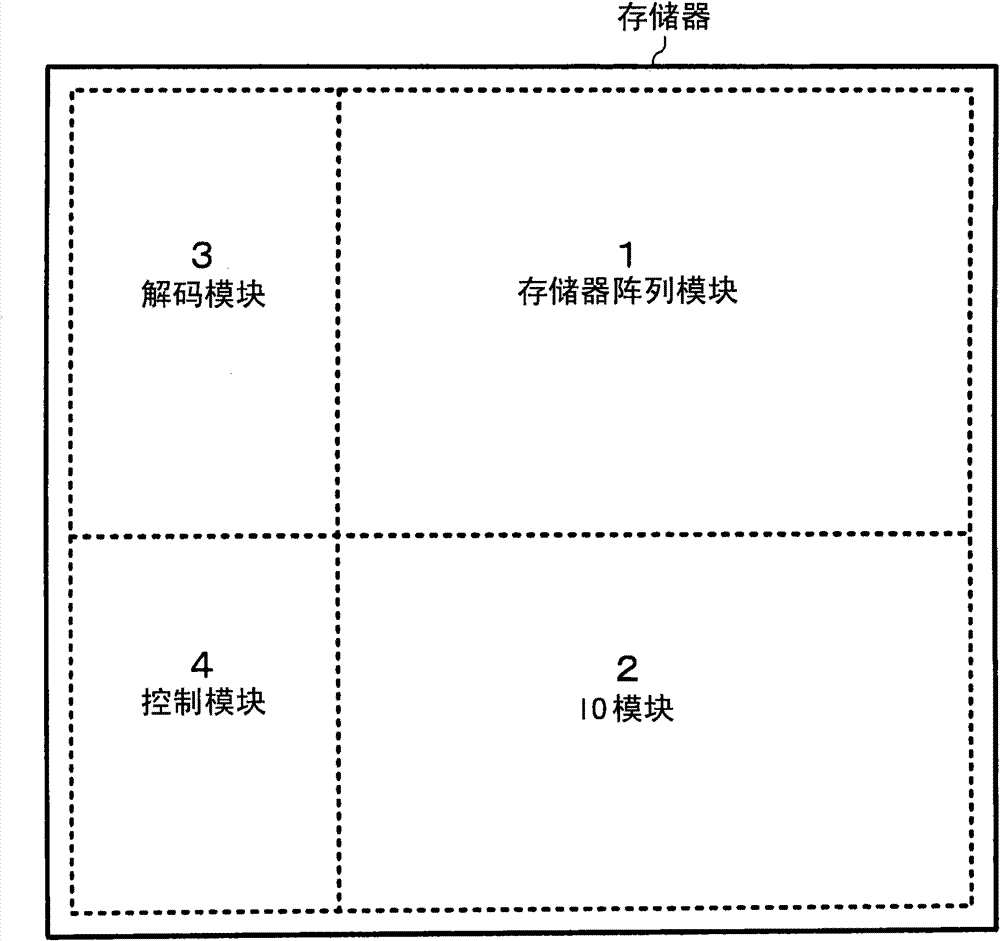

[0055] figure 1 A configuration example of an SRAM module which is one of the semiconductor memory devices according to the present invention is shown. figure 1 The memory array module 1 is a configuration in which a plurality of memory cells are arranged in a matrix, and is equipped with an IO module 2 arranged for a column of the memory array module 1, and a decoding module 3 arranged for a row of the memory array module 1, and is connected with The adjacent positions of the IO module 2 and the decoding module 3 are further configured with a control module 4 .

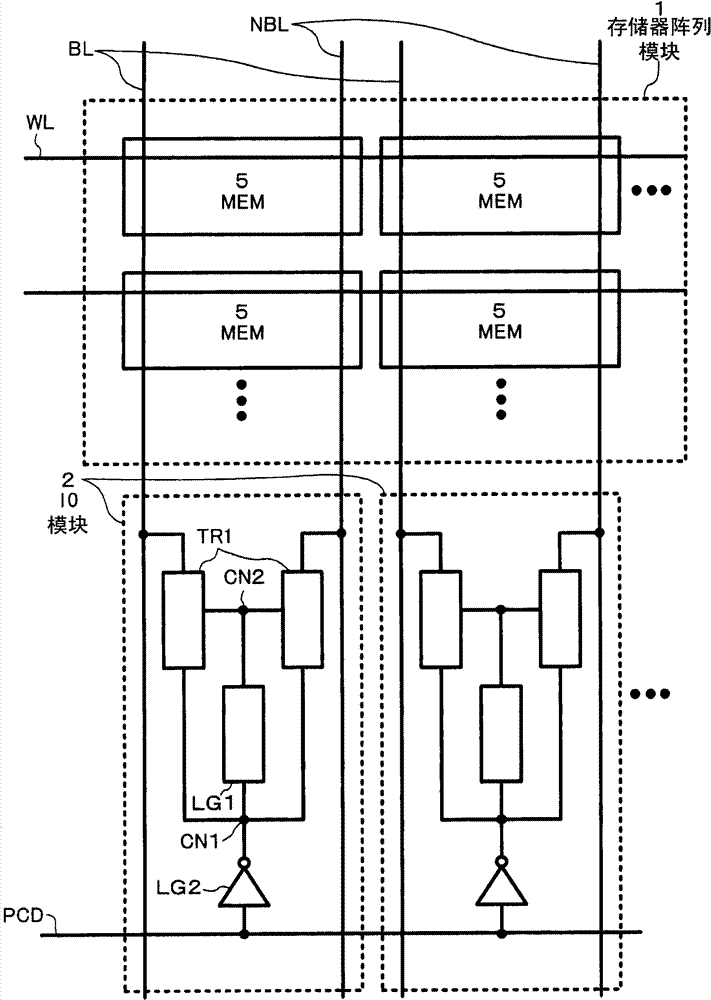

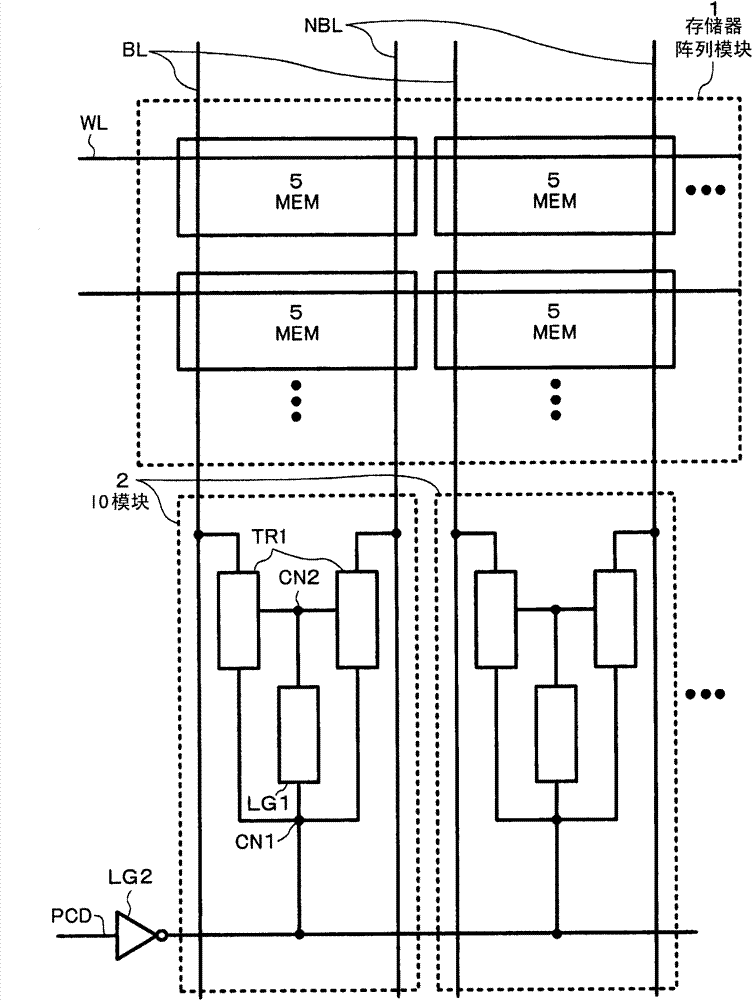

[0056] figure 2 expressed figure 1 The detailed structure of memory array module 1 and IO module 2. exist figure 2 Among them, the memory array module 1 has: a p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More