Semiconductor memory

A memory and semiconductor technology, applied in the direction of semiconductor devices, static memory, digital memory information, etc., can solve the problems of large number of signal lines, difficult control of characteristics, complex structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

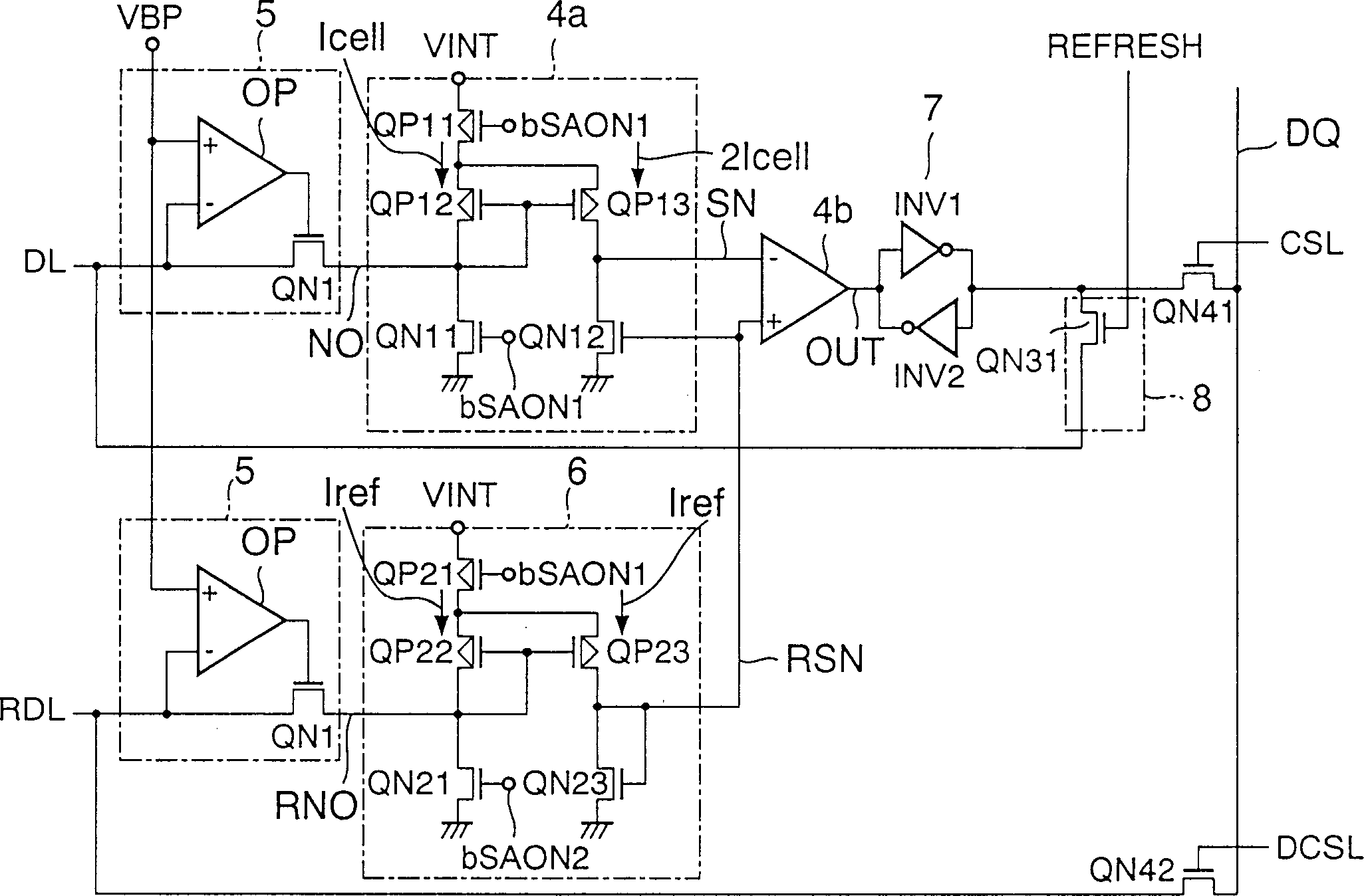

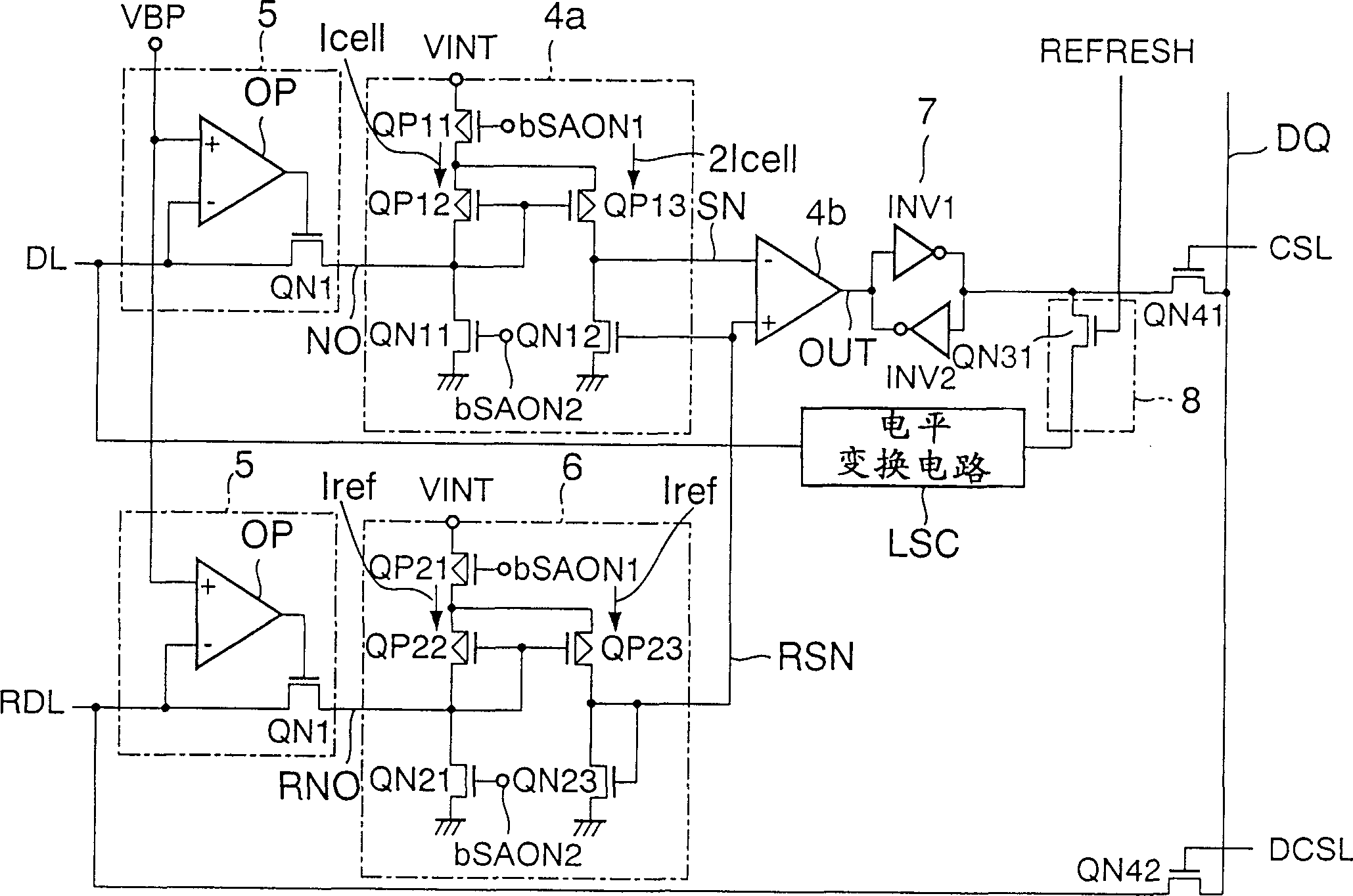

[0026] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

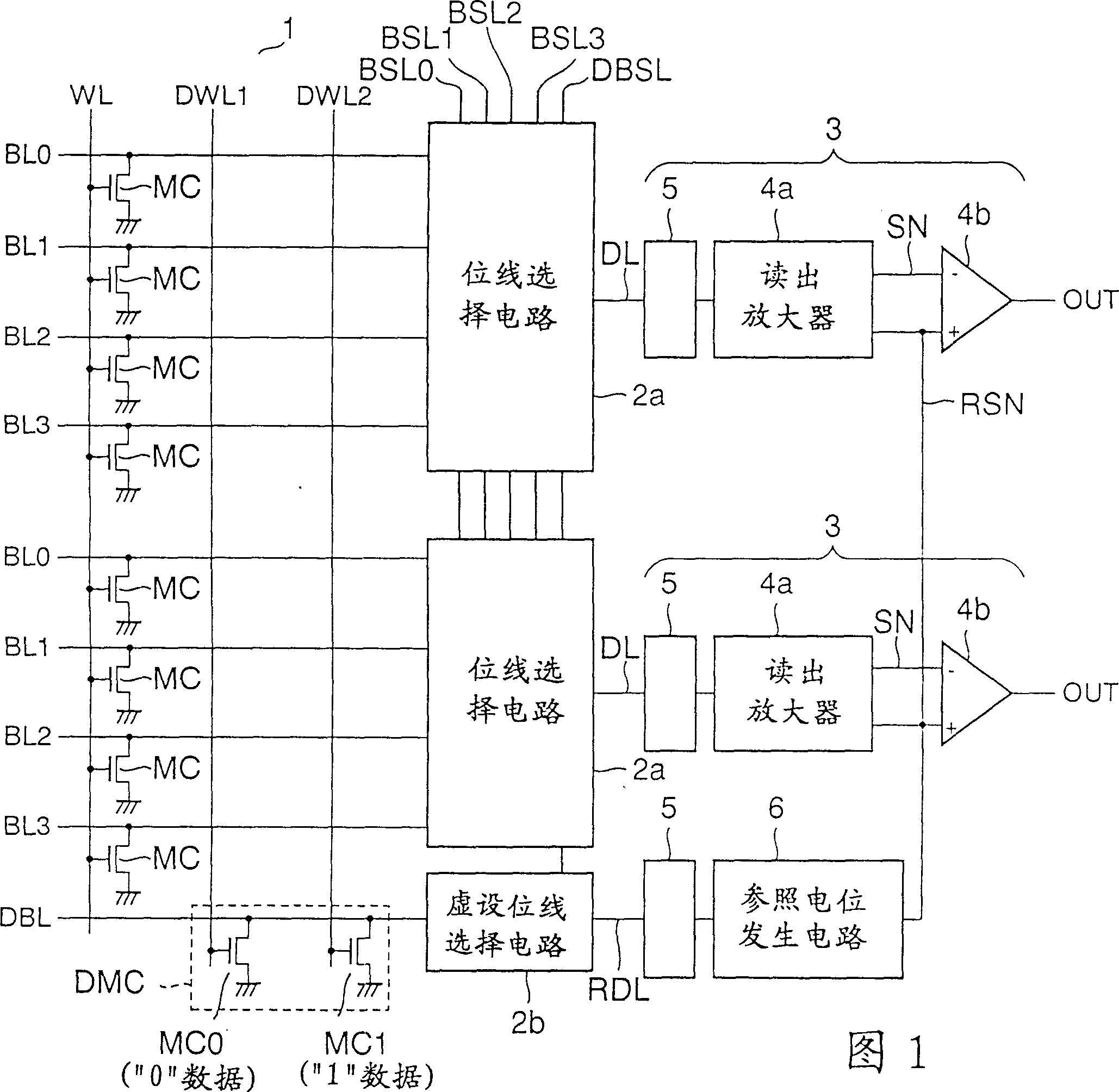

[0027] FIG. 1 shows the structure of a cell array 1 of a DRAM and a data readout circuit 3 connected thereto according to an embodiment of the present invention. DRAM cell MC consists of one MISFET with a floating channel body. Figure 4 The DRAM cell structure in the case of using an n-channel MISFET is shown in . A p-type silicon layer 12 isolated from the silicon substrate 10 by an insulating film 11 such as a silicon oxide film on a silicon substrate 10 is used as a channel body, has a gate electrode 14 formed through a gate insulating film 13, and serves as a source and a drain. n-type diffusion layers 15, 16.

[0028] memory cell array 1 as Figure 5 constructed as shown in. That is, the DRAM cells MC have floating channel bodies that are isolated from other parts, and the source is used as a reference potential (ground potential). The drains of the DRAM cell...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More