Clock switching method and device

A clock switching and clock domain technology, applied in the direction of generating/distributing signals, logic circuits using basic logic circuit components, logic circuits using specific components, etc., can solve problems such as logical confusion, complex operation, and gating output glitches. To achieve the effect of ensuring stability, excellent characteristics, and smooth switching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

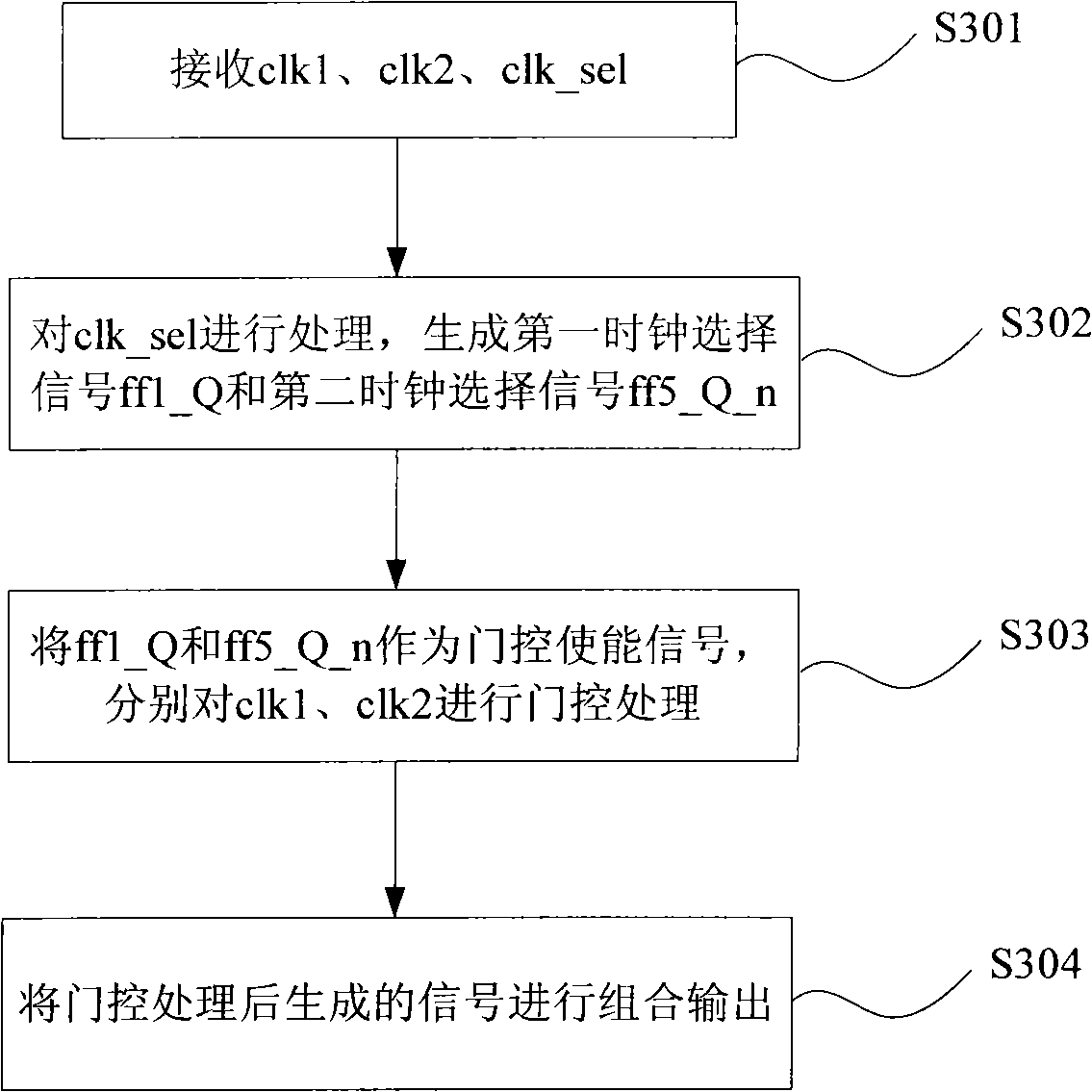

[0044] Embodiment 1, this embodiment proposes a clock switching method, see image 3 shown, including the following steps:

[0045] S301. Receive a first clock signal clk1, a second clock signal clk2, and a clock selection signal clk_sel for switching and outputting the clk1 and clk2.

[0046] S302. Process the clock selection signal clk_sel to generate a first clock selection signal ff1_Q and a second clock selection signal ff5_Q_n.

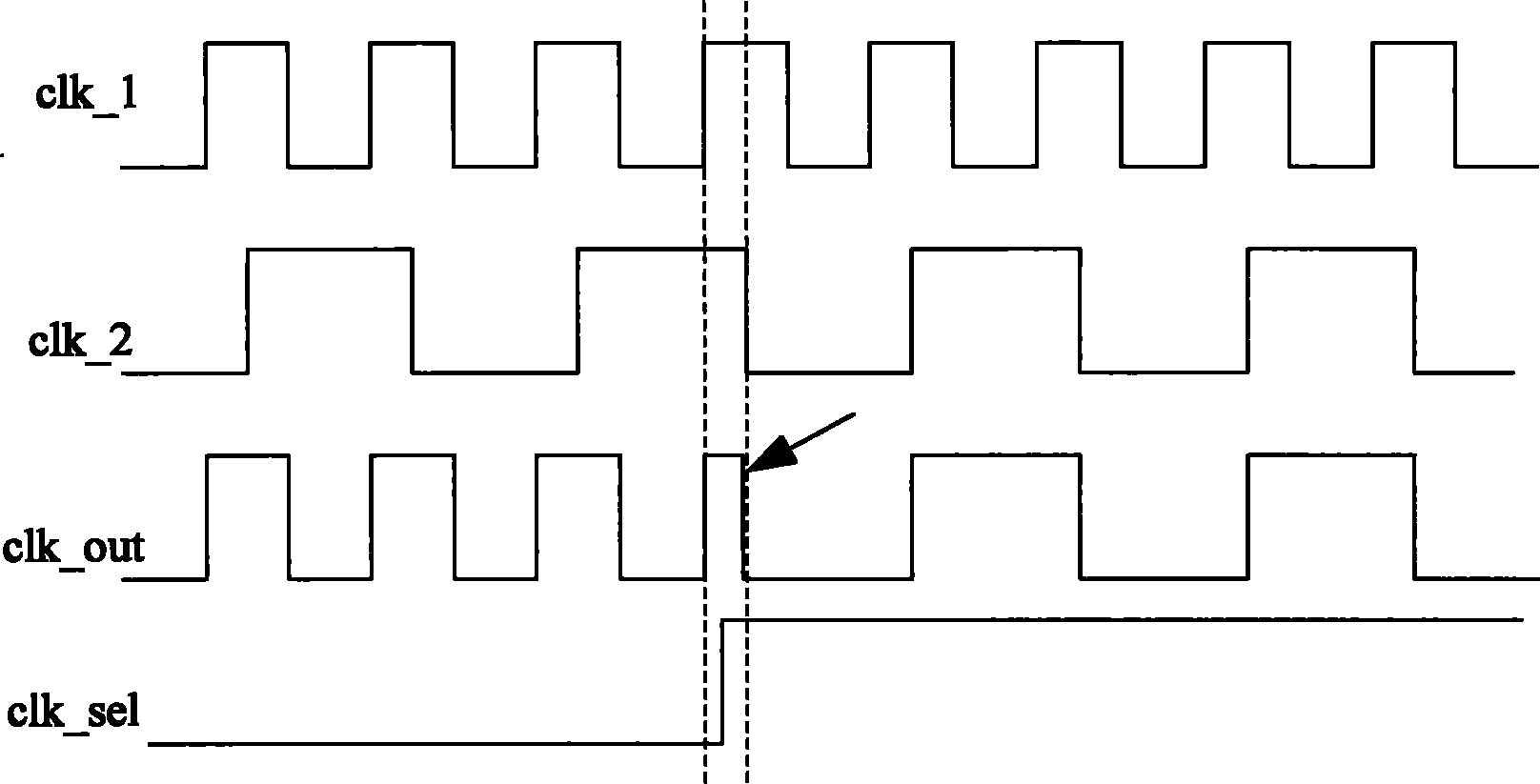

[0047] Among them, ff1_Q is used for enabling control of clk1, and ff5_Q_n is used for enabling control of clk2. When clk_sel is in the state of selecting clk1 output, ff1_Q enters the state of gating clk1 output, and ff5_Q_n enters the state of blocking clk2 output; when clk_sel is in the state of selecting clk2 output, ff1_Q enters the state of blocking clk1 output, and ff5_Q_n enters the state of gating clk2 the state of the output. When clk_sel jumps, in order to avoid glitches or metastable problems in the output clock signal, it is nece...

Embodiment 2

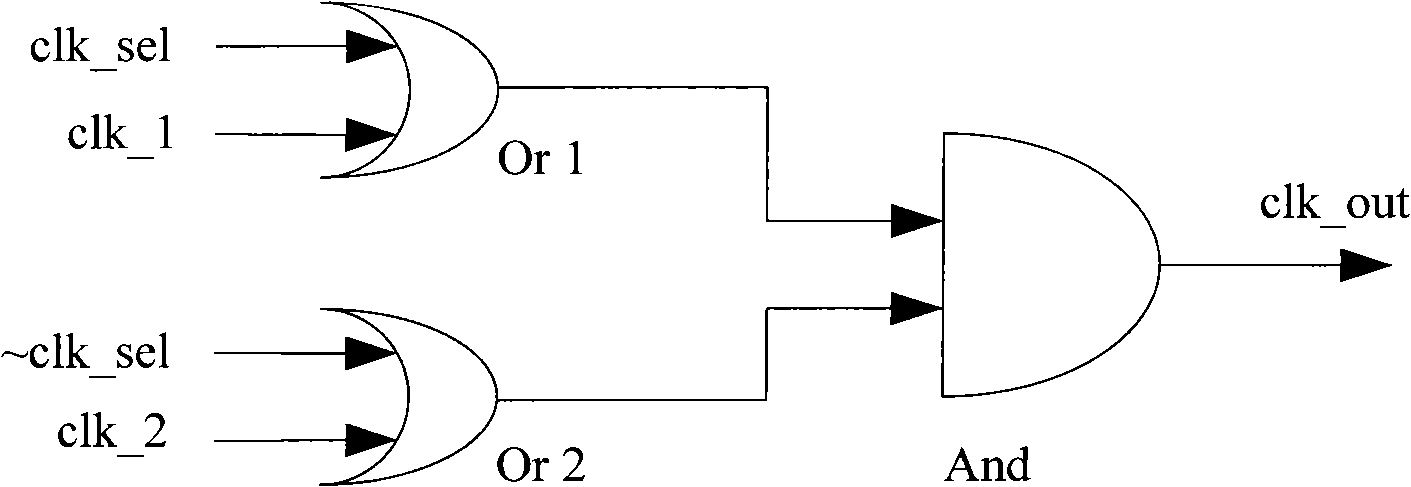

[0059] Embodiment 2, this embodiment is a hardware circuit architecture diagram proposed to implement the clock switching method described in Embodiment 1, see Image 6 As shown, it includes four groups of D flip-flops D1-D4, a first clock gating processing module U1, a second clock gating processing module U2 and a combined processing module U3. Among them, the first and fourth groups of D flip-flops D1 and D4 work in the first clock domain, that is, their clock terminal CP receives the first clock signal clk1; the second and third groups of D flip-flops D2 and D3 work in the first clock domain The second clock domain, that is, its clock terminal CP receives the second clock signal clk2. The clock selection signal clk_sel output by the system for switching clk1 and clk2 is transmitted to the data terminals D of the first and third groups of D flip-flops D1 and D3 respectively, and is synchronously processed by the first group of D flip-flops D1 to generate the first clock sel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More