Method for realizing static and dynamic random access memory (SDRAM) refresh by using field programmable gate array (FPGA)

A refresh cycle and refresh time technology, applied in information storage, static memory, digital memory information, etc., can solve problems such as huge power consumption, increased circuit design, and increased power consumption of system circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

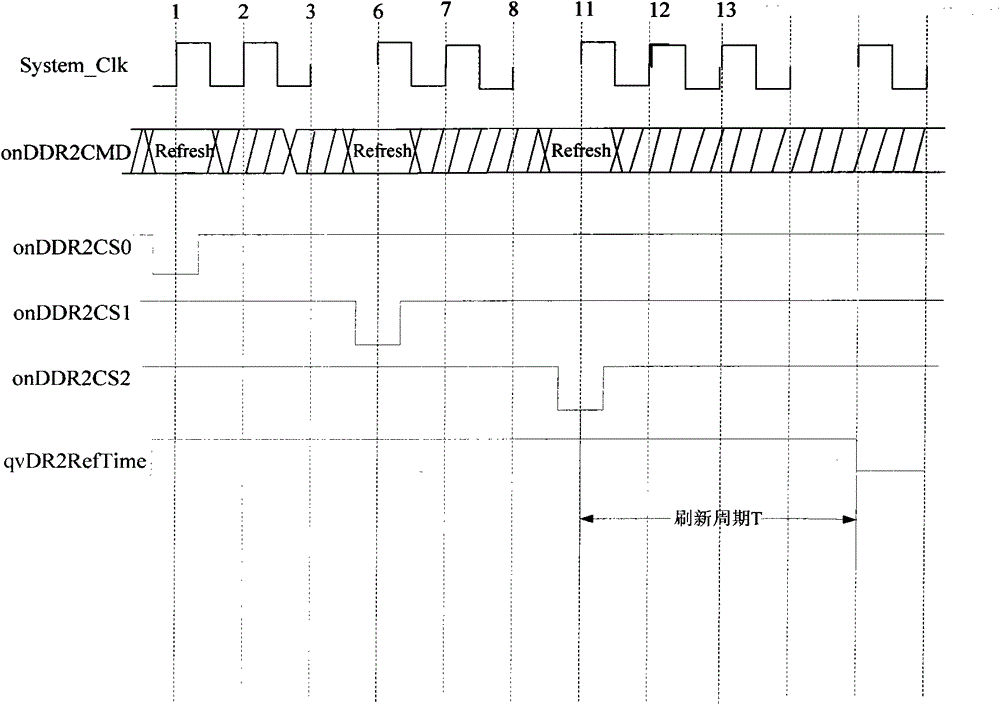

[0016] as attached figure 1 shown. If there are three chip select CSs in the current memory controller that need to be refreshed, when the specified refresh time arrives, as shown in the first clock cycle in the figure, the FPGA sends a refresh command to select the first chip select CS0. The refresh cycle is not over. After CS0 starts to refresh for 5 cycles, issue the second refresh command to select the second chip selection CS1. Also after CS1 strobe refreshes for 5 cycles, issue the third refresh command and select the second chip selection at the same time. The three chip selects CS2, because the memory models are the same, on the premise that the refresh cycle of CS2 is satisfied, the refresh cycles of CS0 and CS1 must also be satisfied. Under normal circumstances, after starting the CS0 refresh, if the refresh period is T, you must wait for the end of the refresh period T before starting the refresh of CS1, and so on, the time required to refresh the three chip select...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More