Non-core layer package substrate and manufacturing method thereof

A core-less, packaged substrate technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as poor coplanarity, difficult tolerance control of volume and height, and damage to semiconductor chip contacts.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The following describes the implementation of the present invention through specific specific examples. Those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

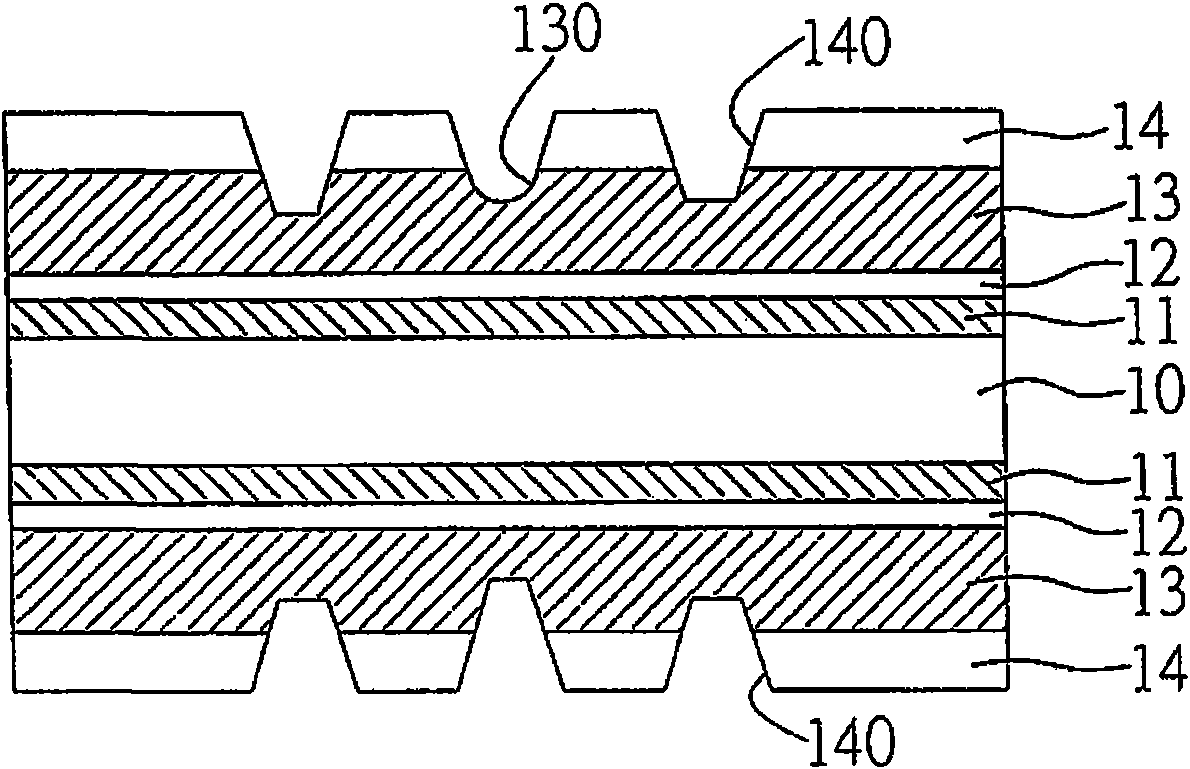

[0072] See Figure 2A to 2K , Is a method for manufacturing a core-less packaging substrate disclosed in the present invention.

[0073] Such as Figure 2A As shown, a substrate 2a is provided, which is composed of a carrier layer 20 having opposite surfaces, a release film 21 partially formed on the opposite surfaces of the carrier layer 20, and an adhesive layer 20a surrounding the area outside the release film 21 , The metal layer 22 formed on the release film 21 and the adhesion layer 20a, a first resist layer 23a formed on the metal layer 22, and an auxiliary dielectric layer 24 formed on the first resist layer 23a , And an effective area A is defined on each auxiliary dielectric layer 24; wherein the area of the ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More