High-voltage insulation type LDNMOS (laterally diffused metal oxide semiconductor) device and manufacture method thereof

A high-voltage isolation and high-voltage technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., to achieve the effects of reducing source-drain on-resistance, improving device breakdown, and flattening electric field distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

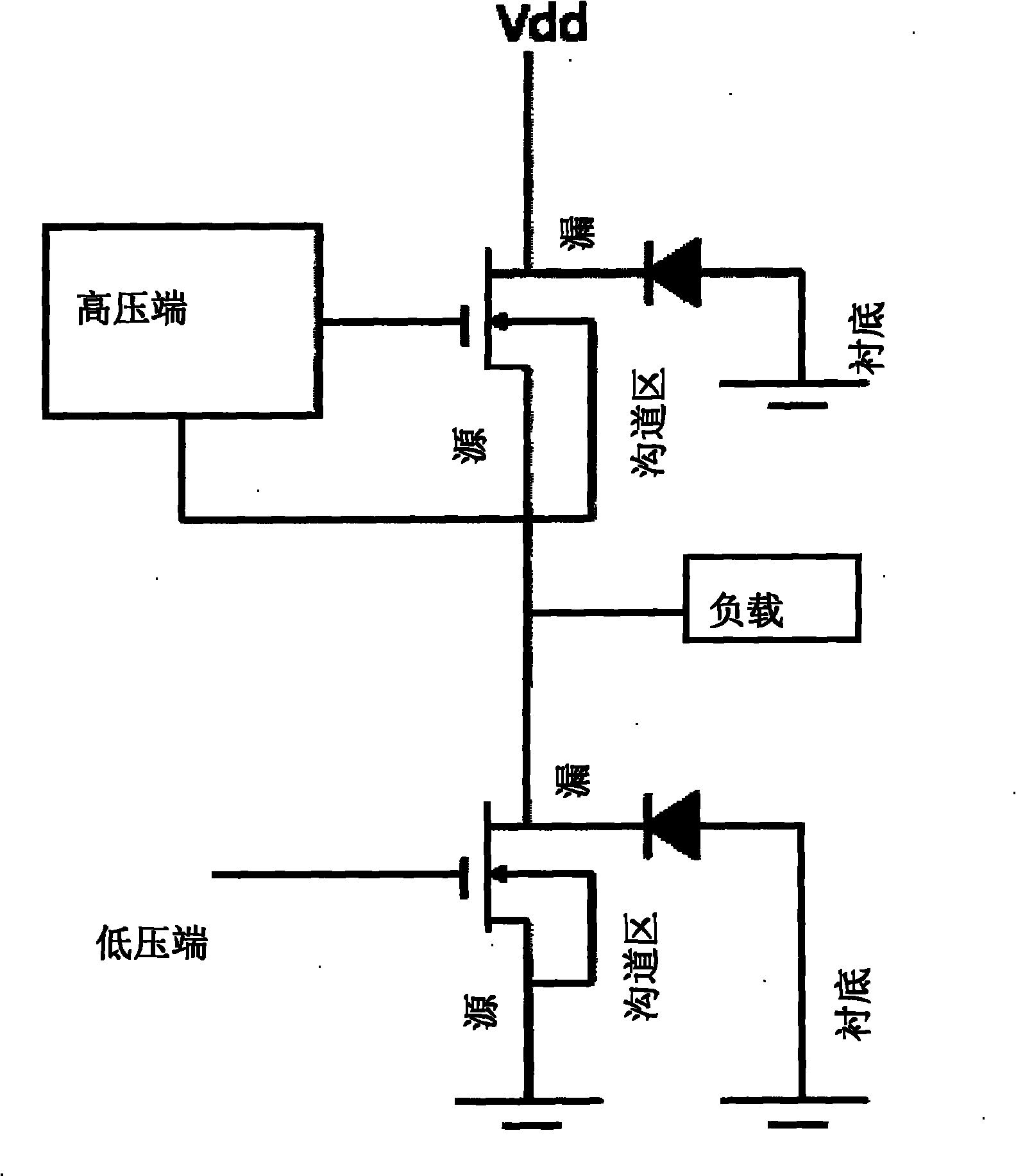

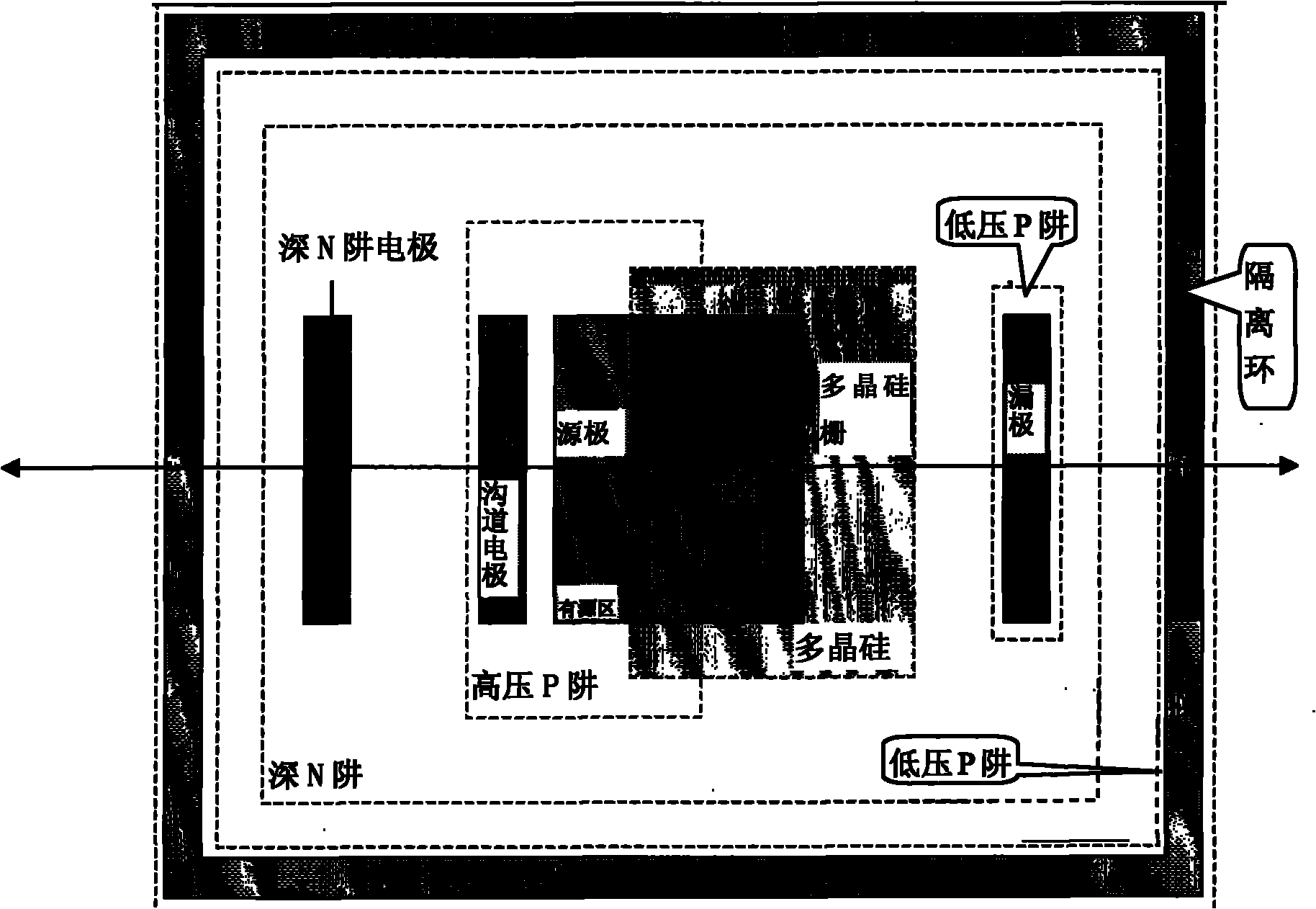

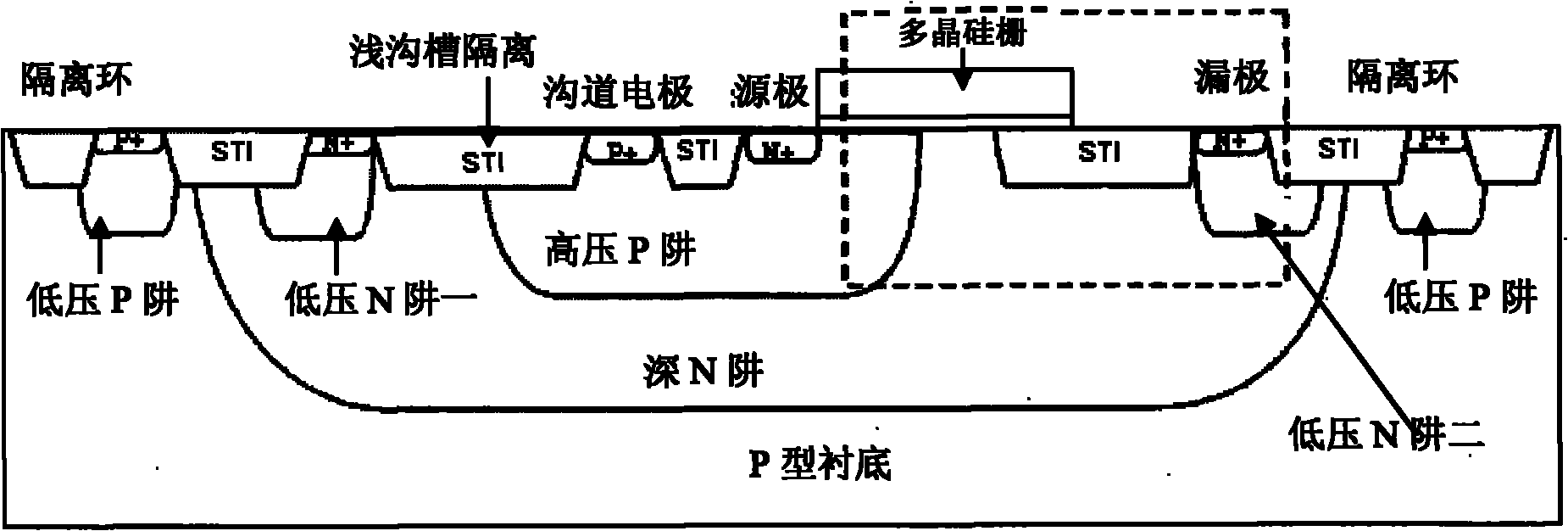

[0032] Such as Figure 6 As shown, it is a plan view of a high voltage isolation type LDNMOS device of the present invention; as Figure 7 Shown is a cross-sectional view of the high-voltage isolation LDNMOS device of the present invention. The high-voltage isolated LDNMOS device provided by the present invention includes: a P-type substrate, and the substrate electrode is drawn out through a low-voltage P well formed in the substrate and then made into a P+ ohmic contact, and the substrate electrode forms an isolation ring (Isolation Ring) ; a deep N well, the electrode of the deep N well is drawn out through a low-voltage N well as an N+ ohmic contact; a channel region is formed by a high-voltage P well formed in the deep N well, and is drawn out through a P+ ohmic contact A channel electrode; a source region, composed of an N+ doped region formed in the channel region, directly making an ohmic contact to lead out the source; a drain region, formed in a low-voltage N well 2 f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More