IC (integrated circuit) function verification method

A function verification and normalization technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problem of memory space explosion, no way to measure function coverage, function coverage cannot be effectively guaranteed, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

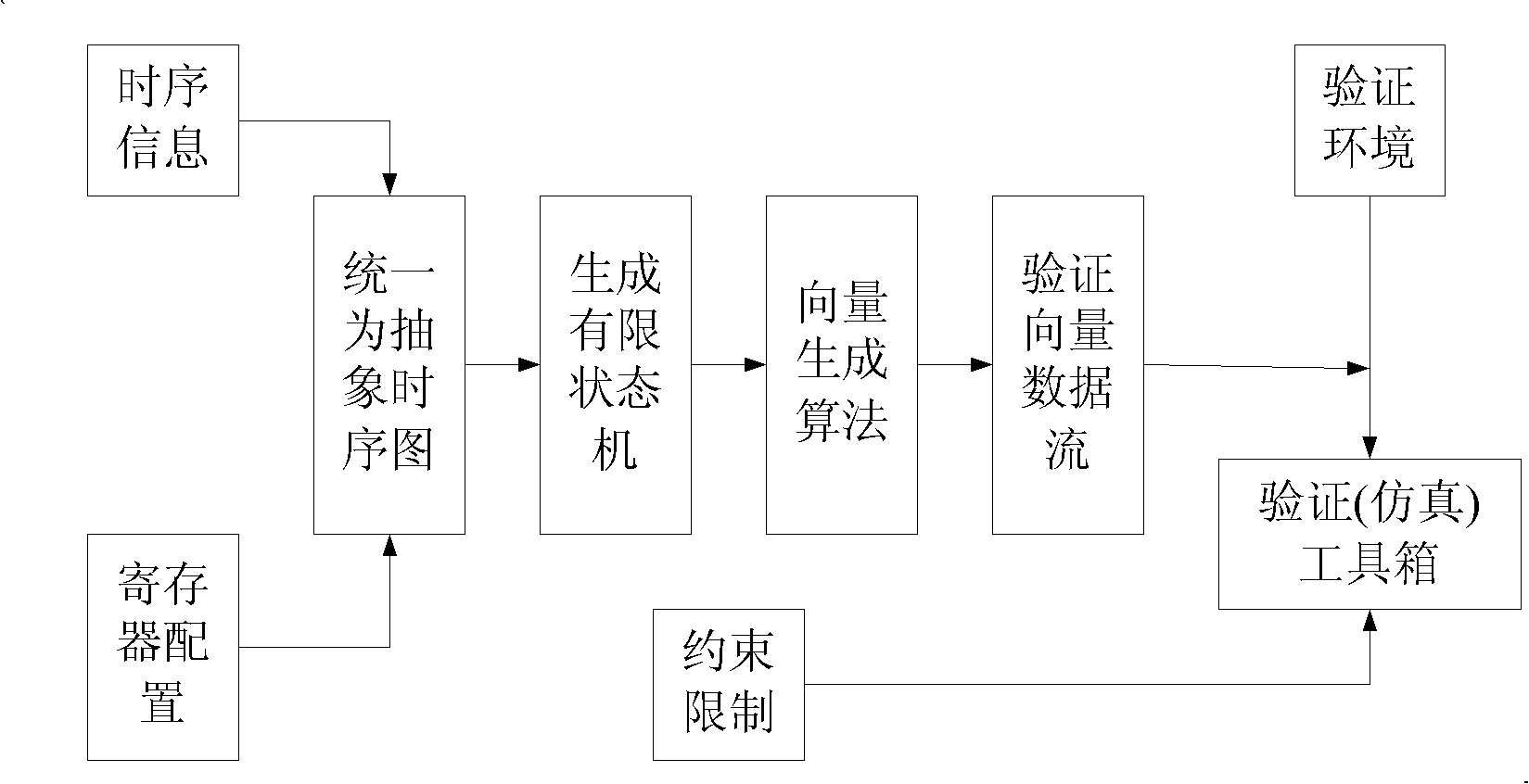

[0044] According to the scheme technical route architecture of the method of the present invention, the following will be further described in detail in conjunction with specific embodiments. The specific embodiments described here are not limitations of the present invention, but explanations of the present invention. The specific implementation methods are as follows: the process is as follows image 3 shown.

[0045]1. Unify the internal register configuration information and external interface timing of the design under test into a normalized timing diagram.

[0046] The key to this step is to incorporate the internal register configuration into the timing diagram of the external interface.

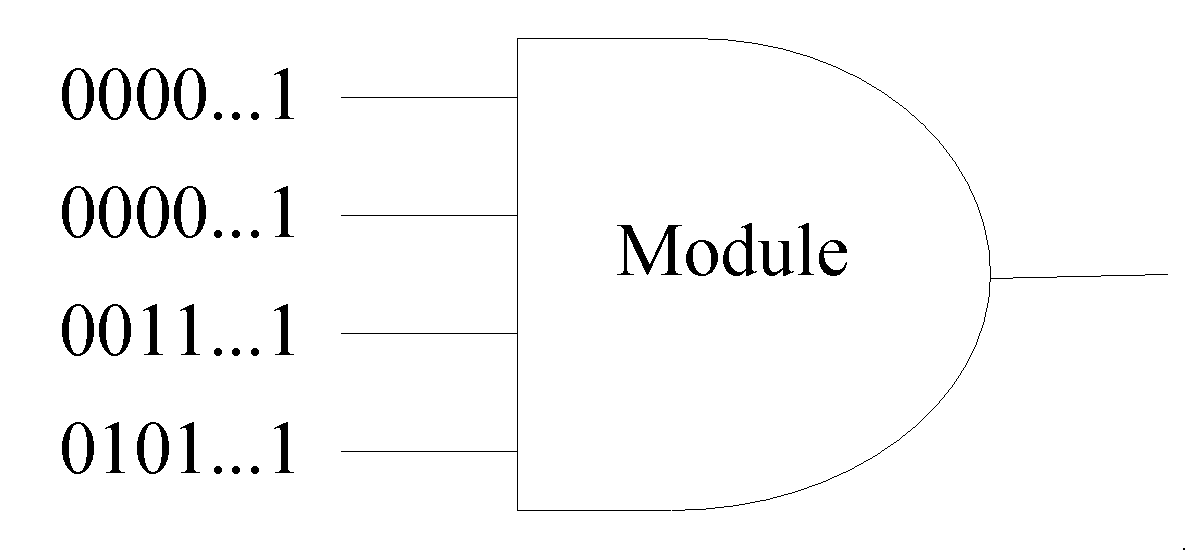

[0047] What we know is the interface timing diagram reflecting its external characteristics and the configuration information of registers reflecting its internal state in the interface specification of the module to be tested. In order to achieve unification, we hope to incorporate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More