Saber-based circuit failure simulation analyzing method

A circuit fault and simulation analysis technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems that analog circuits cannot be simulated, faults cannot be simulated, etc., and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

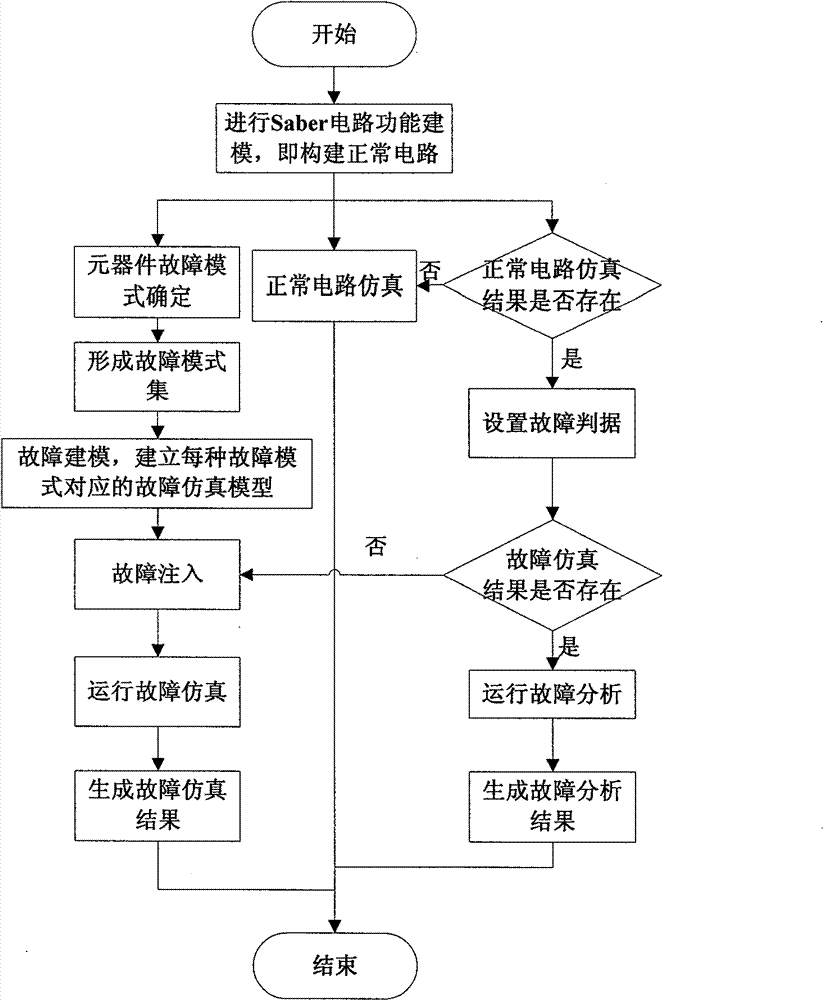

Method used

Image

Examples

Embodiment example 1

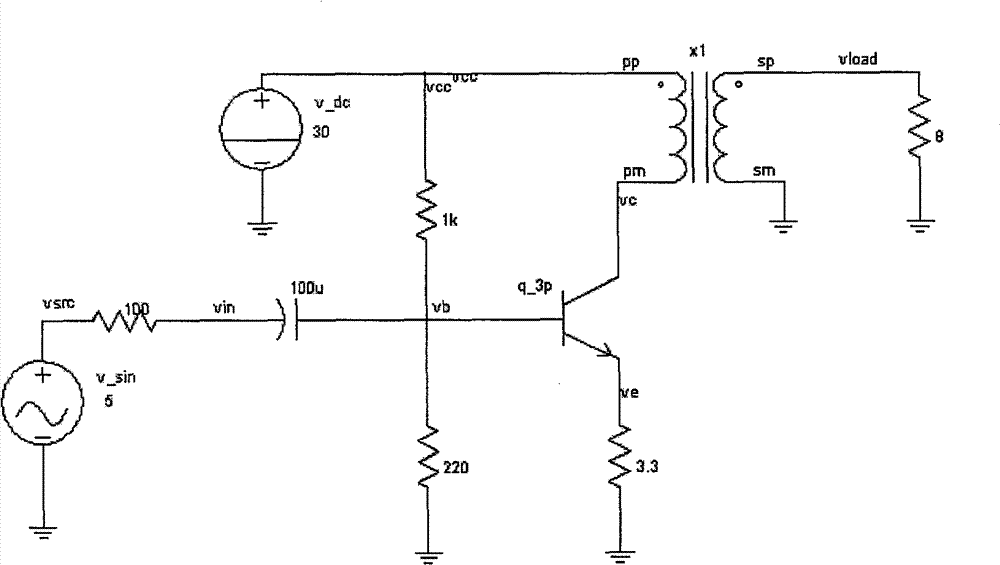

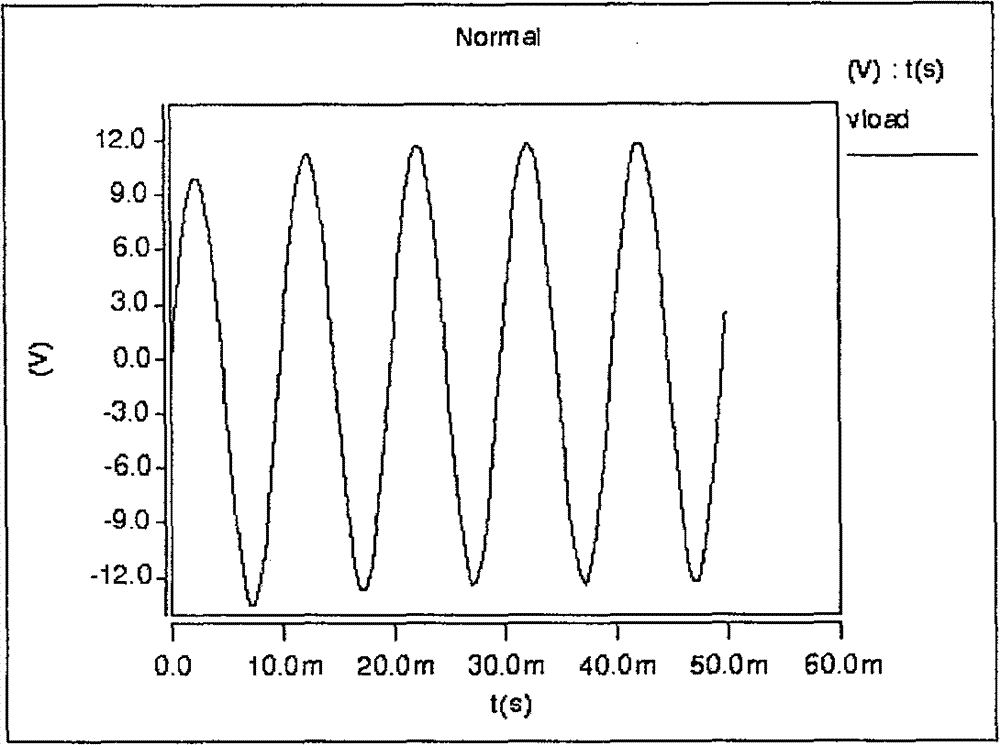

[0142] An amplifying circuit is used to illustrate the fault simulation analysis method. The schematic diagram of the amplifying circuit is shown in figure 2 As shown, the waveform of the normal simulation output vload of the circuit is as follows image 3 As shown, the amplitude is a sine wave around plus or minus 12v.

[0143] The steps of the case implementation process are the above seven steps. For this case, for the failure mode selected in step 2, three failure modes, such as base-collector short circuit, base open circuit, and gain degradation, were selected for bipolar transistors; for transformers, pp pin open circuit, pp, pm were selected There are three failure modes of pin short circuit and parameter drift. After step five, the simulation results of each failure mode are obtained, as shown in Table 3. Step 6 There are two methods of fault criterion setting: waveform discrimination method and parameter discrimination method. In the waveform discrimination meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More