Clock frequency multiplier, device and clock frequency multiplication method

A technology of clock frequency multiplication and frequency multiplication, which is applied in pulse processing, electrical components, pulse technology, etc., and can solve problems such as error-prone, clock output signal cycle changes, and logic errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

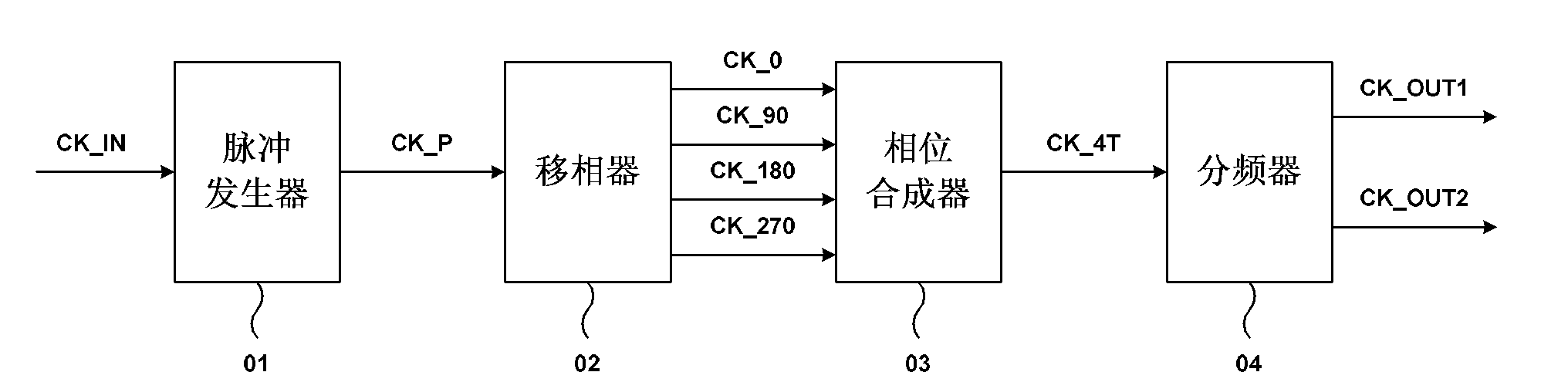

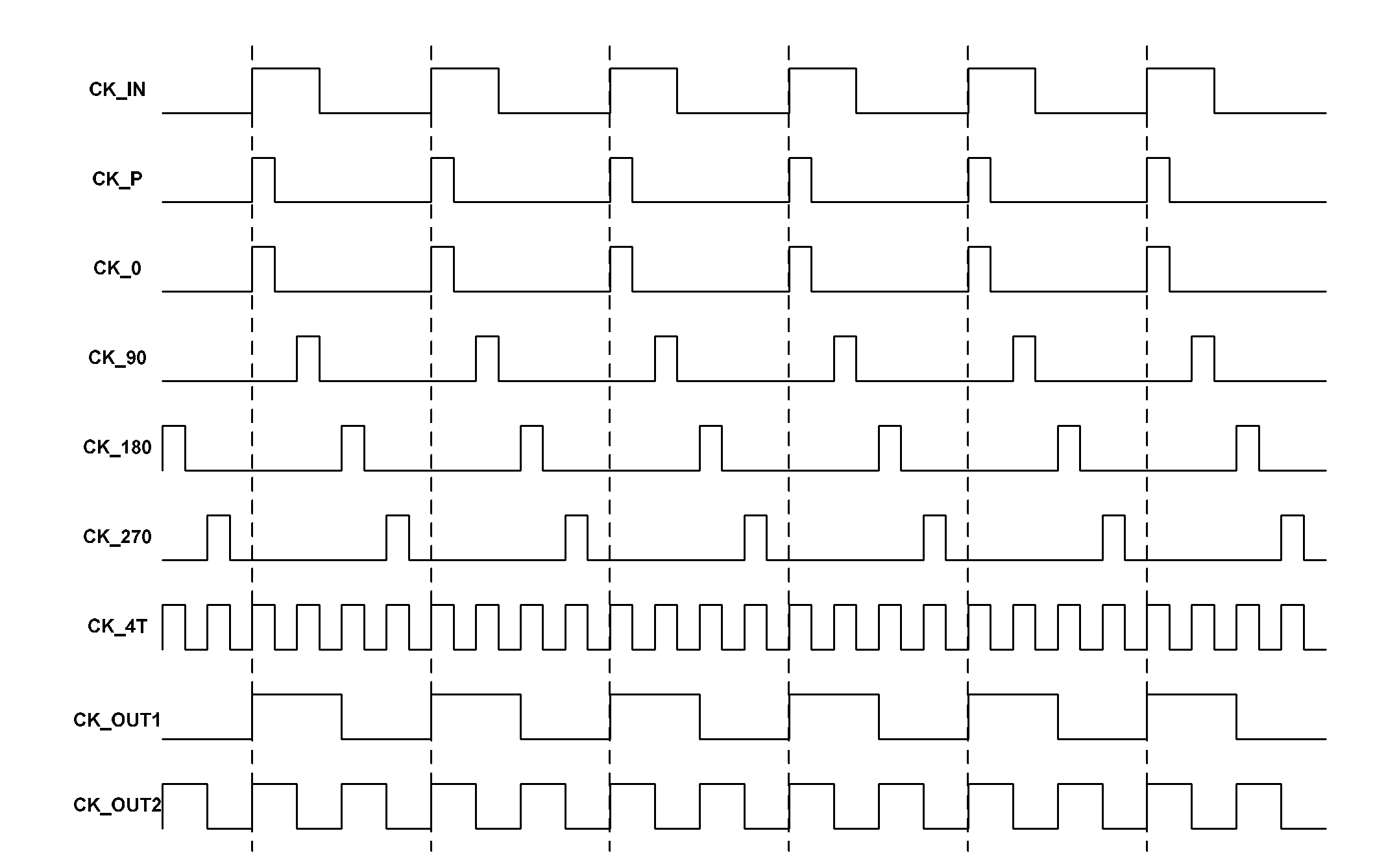

[0100] Embodiment 1: A clock frequency interrogator

[0101] As a preferred implementable mode, since the storage unit and calculation unit of some microprocessors use different clock domains, an on-chip clock source including a clock multiplier is required to generate clocks with good duty cycles at different frequencies Signal. Therefore, in the embodiment of the present invention, the clock frequency multiplier and device and the clock frequency multiplication method of the embodiment of the present invention are applied to the Loongson No. 1 microprocessor, and the external crystal oscillator signal provides the circuit with a clock signal with a frequency of 50-100 MHz , and the duty cycle is not ideal at 50%. After frequency multiplication processing, a double frequency clock signal is generated as an example for detailed description.

[0102] However, it should be noted that the clock frequency multiplier and device and clock frequency multiplication method of the pres...

Embodiment 2

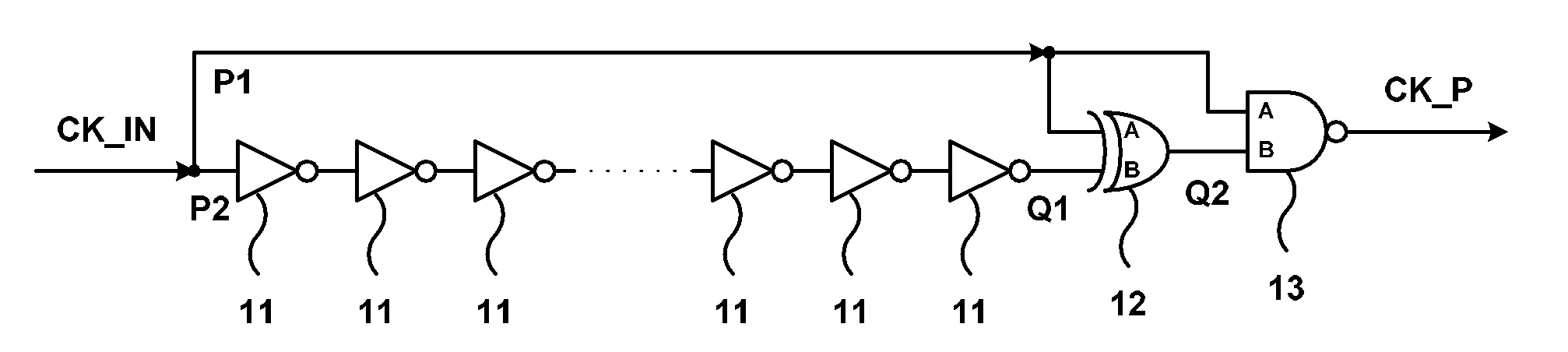

[0187] Embodiment 2: An improved clock period measurement unit

[0188] In the embodiment of the present invention, the D-type flip-flop can be implemented by using a D-type transistor as a sampling tool, and its output result is a number of continuous 1 signals followed by a number of continuous 0 signals. The signal becomes a 1 signal, as long as it is not at the junction of the 1 signal and the 0 signal, it has no effect on the circuit. However, if the latch state of the 1 signal changes from a 1 signal to a 0 signal, the delay in the digitally controlled delay 23 will be changed, thereby causing an error.

[0189] Therefore, in the embodiment of the present invention, as another possible implementation mode, the embodiment of the present invention provides a clock period measurement unit, such as Figure 13 shown.

[0190] As another possible implementation, a clock period measurement unit in the embodiment of the present invention includes four two-input NAND logic gate...

Embodiment 3

[0193] Embodiment 3: An improved two-input NAND logic gate circuit device, and an improved non-logic gate circuit device

[0194] When the threshold voltage of the N-type field effect transistor drifts downward, the N-type field effect transistor in the logic gate circuit will be easily turned on, thereby changing the working state of the circuit. Therefore, in the embodiment of the present invention, as another possible Embodiments provide a two-input NAND logic gate circuit device, such as Figure 15 shown; and a non-logic gate circuit device, such as Figure 14 shown.

[0195] In the embodiment of the present invention, as another possible implementation mode, such as Figure 14 As shown, the non-logic gate circuit device 16 of the embodiment of the present invention is composed of two N-type field effect transistors and two P-type field effect transistors.

[0196] The N-type field effect transistor substrate is connected to VSS, the P-type field effect transistor subst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More