Manufacturing method of super-junction semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reduced withstand voltage reliability and withstand voltage, and achieve the effect of preventing the drop in the withstand voltage qualified product rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

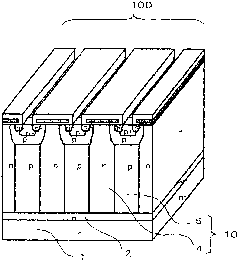

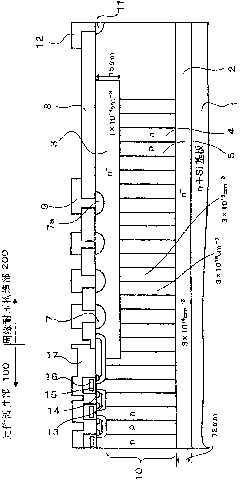

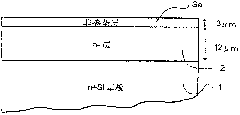

[0061] In Example 1, a method of manufacturing a super junction MOSFET will be described. Figure 3 ~ Figure 12 is expressed in order figure 1 , 2 A cross-sectional view of the main part of the manufacturing process of the super junction semiconductor device (super junction MOSFET) shown. Such as image 3 As shown, at high concentrations n + Si substrate 1 is grown by low-doping epitaxy, for example, 3×10 is formed with a thickness of about 12 μm 14 cm -3 low concentration n - Layer 2, on which an undoped n-layer 3a is formed by epitaxial growth, for example, to a thickness of 3 μm. On the surface of the non-doped n-layer 3a, alignment marks (alignment marks, not shown) required for correct overlapping of each stage of the multi-stage epitaxial layer in the subsequent process are formed.

[0062] Such as Figure 4 As shown, on the above-mentioned non-doped n-layer 3a, an n-type impurity such as phosphorus is ion-implanted 4a on the entire surface at the depth indicate...

Embodiment 2

[0069] In embodiment 2, for having in n + Si substrate 1 and low concentration n - The superstructure structure 10 in which n-type and p-type columns are alternately arranged on the layer 2 has n - A super-junction semiconductor device with a low-concentration epitaxial layer 3 illustrates a manufacturing method different from that of Embodiment 1.

[0070] Figure 3 ~ Figure 12 is expressed in order figure 1 , figure 2 A cross-sectional schematic view of the manufacturing process of the super junction semiconductor device (super junction MOSFET) shown. In the same manner as in Example 1, a super junction MOSFET was fabricated. The difference from the manufacturing method of the super junction MOSFET in Example 1 is that in Example 2, in n - When growing the low-concentration epitaxial layers 3e, 3f, and 3g, the hydrogen annealing temperature and the low-doped epitaxial growth start temperature are lower than 1100°C. However, once the epitaxial growth starts, since the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More