P type metal oxide semiconductor transistor for plasma display panel (PDP) driving chip

A technology for driving chips and semiconductor tubes, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of easy breakdown of N-type epitaxial layers, and achieve the effects of saving chip area, fully compatible processes, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

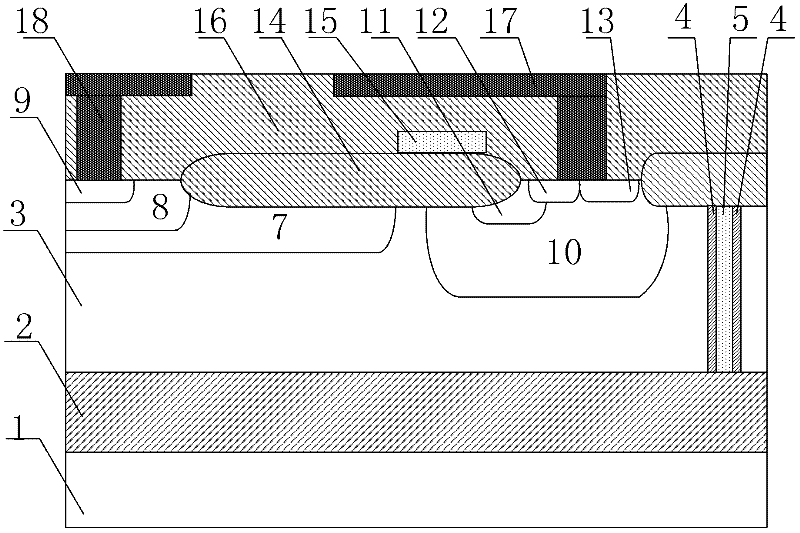

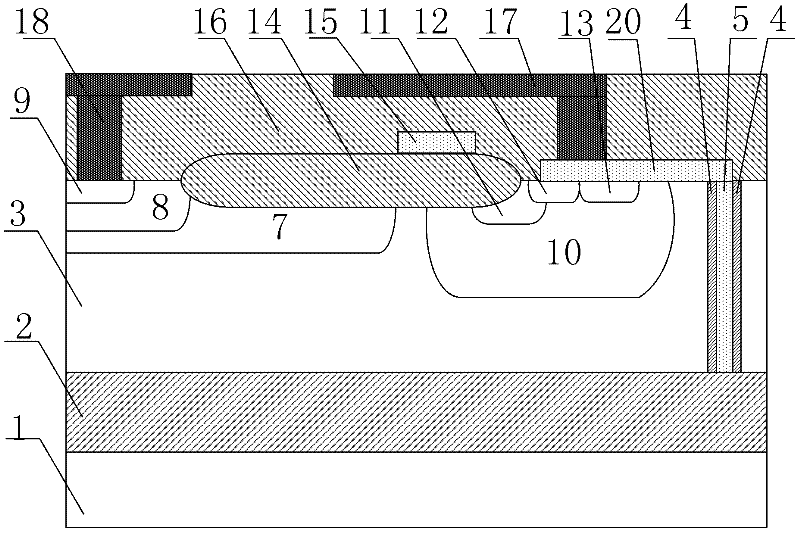

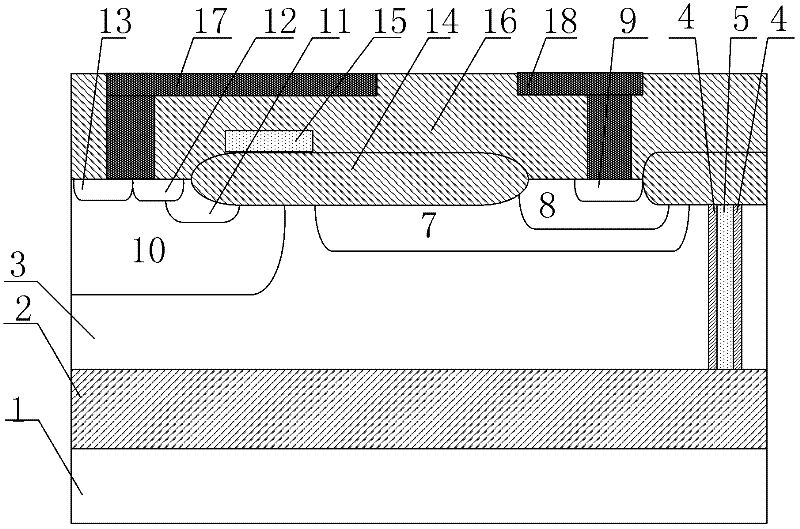

[0016] The cross-sectional view of the P-type metal oxide semiconductor tube of the PDP driver chip in this example is as follows image 3 .

[0017] The upper surface of the P-type drain end ohmic contact region 9 of the P-type metal oxide semiconductor transistor of the PDP driver chip is connected to the drain end metal 18, and the rest is arranged in the P-type buffer area 8, and the P-type buffer area 8 is arranged in the In the high-voltage P-type well 7, the isolation trench is arranged between the field oxide layer 14 and the buried oxide layer 2 at the drain position in the N-type epitaxial layer 3, and the horizontal distance between the isolation trench and the high-voltage P-type well 7 is not 0, and every Each isolation trench is composed of a polysilicon layer 5 and two sidewall oxide layers 4, wherein a polysilicon layer 5 is arranged between the field oxide layer 14 and the buried oxide layer 2 at the drain position in the N-type epitaxial layer 3, and the poly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More